Verilog code for different flipflops - mbits-mirafra/digitalDesignCourse GitHub Wiki

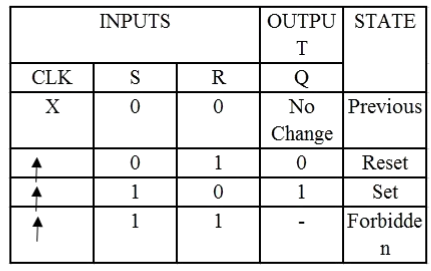

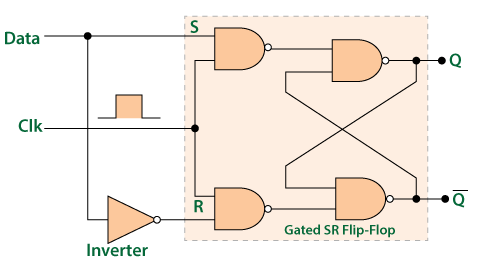

SR flipflop (Gate Level)

module srff(q, qbar, s, r, clk);

input s,r,clk;

output q, qbar;

wire nand1_out; // output of nand1

wire nand2_out; // output of nand2

nand (nand1_out,clk,s);

nand (nand2_out,clk,r);

nand (q,nand1_out,qbar);

nand (qbar,nand2_out,q);

endmodule

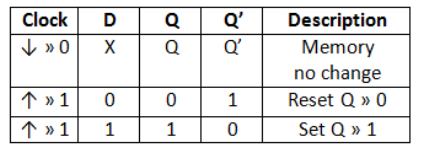

D flipflop (Behavioral model)

module dff(d,clk,q,qbar);

input d, clk;

output reg q, qbar;

always@(posedge clk)

begin

q <= d;

qbar <= !d;

end

endmodule

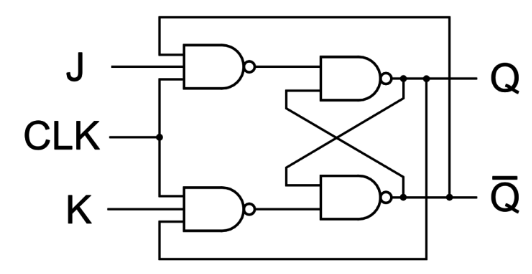

JK flipflop (Gate level)

module jkff(q,qbar,clk,j,k);

input j,k,clk;

output q,qbar;

wire nand1_out; // output from nand1

wire nand2_out; // output from nand2

nand(nand1_out, j,clk,qbar);

nand(nand2_out, k,clk,q);

nand(q,qbar,nand1_out);

nand(qbar,q,nand2_out);

endmodule