NON Restoring Division - mbits-mirafra/digitalDesignCourse GitHub Wiki

Steps included

- Initialize

- Shift

- Addition/subtraction

- Set Q0

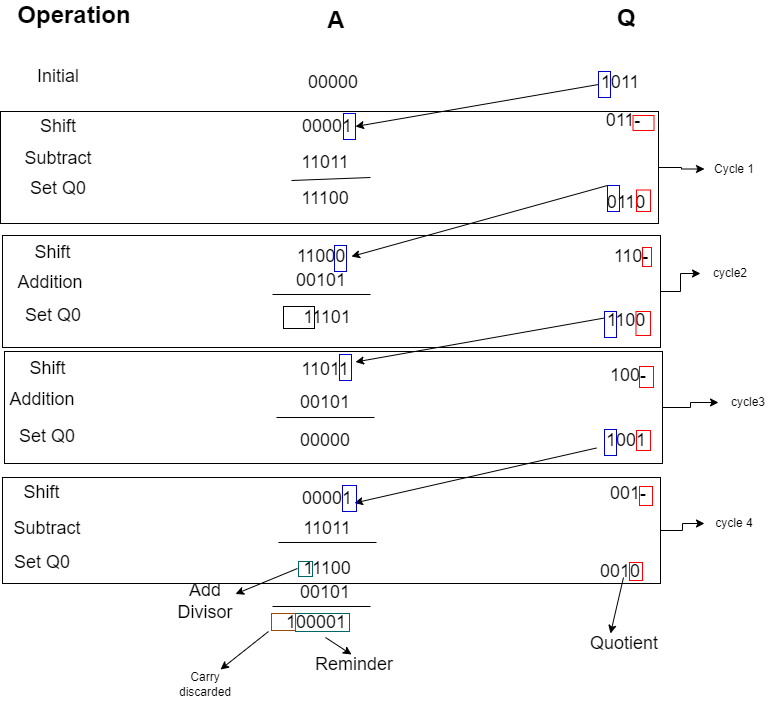

The steps 2 to 4 are repeated n times. (n - number of bits in Dividend)

1. Initially

Q register -A ‘n’ bit Dividend is initialized B register - Divisor is given B register. The Number of bits in the divisor must be equal to ‘n+1’. If not equal 0’s are added to MSB. A register - initialized to 0 with n+1 bits.

Ex: dividend - 1011 Divisor - 101 In Q register —- 1011 (n=4) In B register — 00101 (n+1=5) A register — 00000

2. Shift

It referred to left shifting of A and Q register

3. Addition / subtraction

Based on the MSB of A register after shifting operation addition or subtraction is performed

If MSB of A register is 1 - divisor is added to A register If MSB of A register is 0 - divisor is subtracted from A register

4. Set Q0

Based on the value of MSB of A register after addition/ subtraction Q0 is set either 1 or 0

If MSB of A register is 1 - Q0 is set to 1 If MSB of A register is 0 - Q0 is set to 0

After n cycle if the MSB of A register is 1 then divisor must be added to it to get the final value of A register. Otherwise Its the final value.

Finally the number in A register is Reminder The number in Q Register is Quotient.

Example - Divisor - 101 & Dividend - 1011

here n = 4

In B register Divisor is stored as 00101 (n+1)

Q register - 1011

A Register - 00000

2's complement of divisor - 11011 (for subtraction)