Latches with Asynchronous Enable - mbits-mirafra/digitalDesignCourse GitHub Wiki

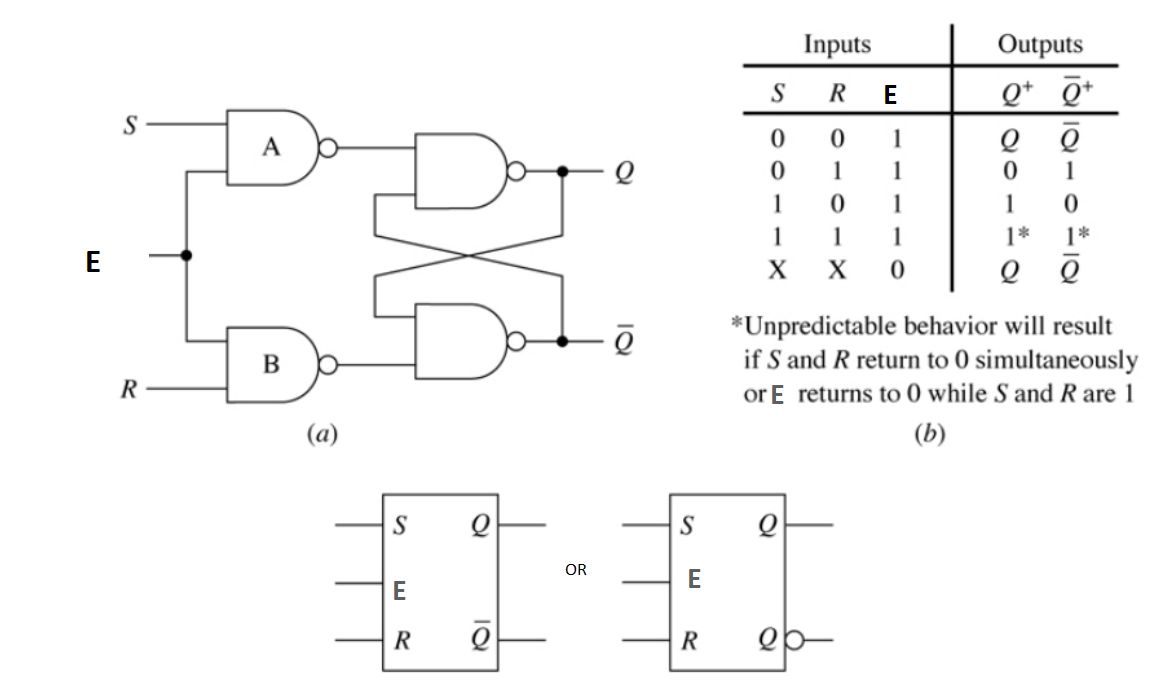

Gated S-R Latch

A Gated SR Latch is a special type of SR Latch having three inputs, i.e., Set, Reset, and Enable. The enable input must be active for the SET and RESET inputs to be effective.

The ENABLE input of gated SR Latch enables the operation of the SET and RESET inputs.This ENABLE input connects with a switch.

The Set-Reset inputs are enabled when this switch is on. Otherwise, all the changes are ignored in the set and reset inputs.

The logical circuit of a Gated SR Latch and truth table are shown below.

Working:

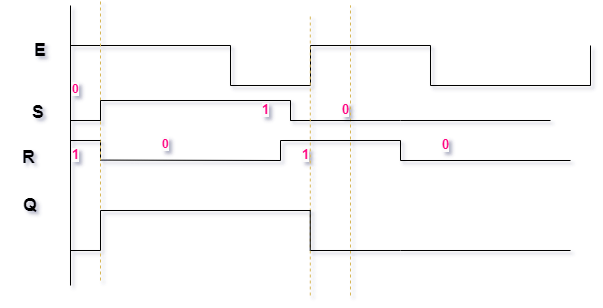

Timing Diagram:

Gated D Latch

The output of the latch is the same as the input passed to the Data input when the ENABLE input is set to 1. At that time, the latch is open, and the path is transparent from input to output. If the ENABLE input is set to 0, the D latch's output is the last value of the latch, i.e., independent from the input D, and the latch is closed.

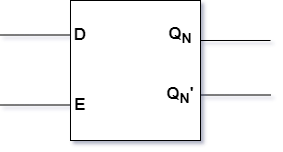

Block Diagram:

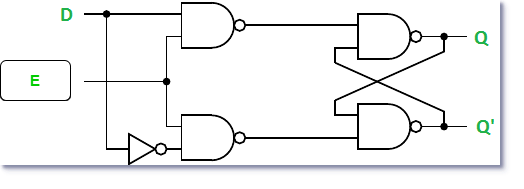

Circuit diagram:

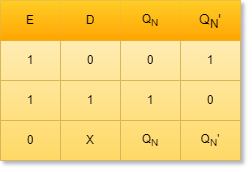

Truth table:

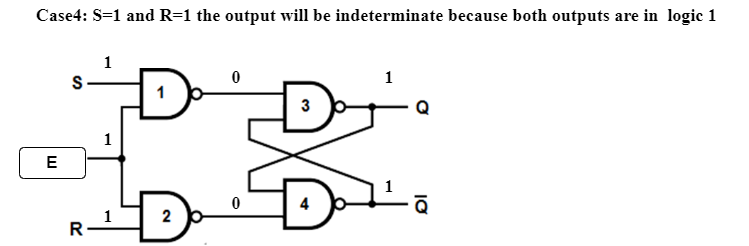

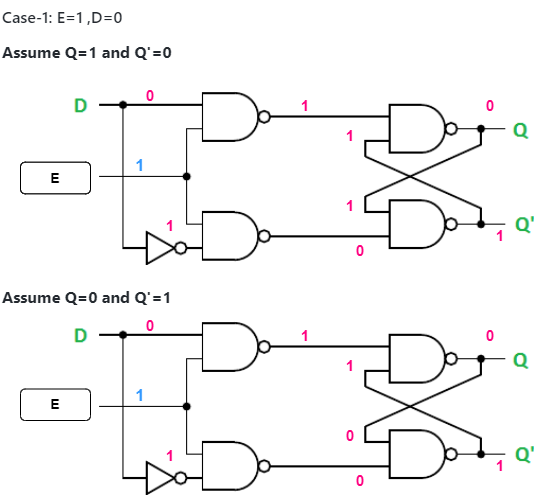

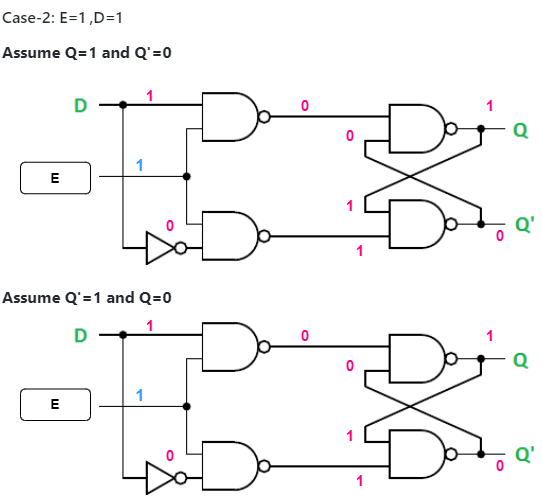

Working:

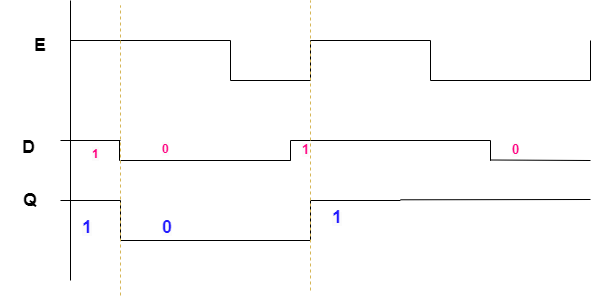

Timing diagram:

Gated J-K Latch

The Latches in which the output is fed back to the input is known as a J-K latch. The condition of the state under ambiguous has been eliminated in this circuit. When both the inputs J and K are HIGH the output states get toggled. It is similar to the basic S-R gate. The only difference is the feedback path application.

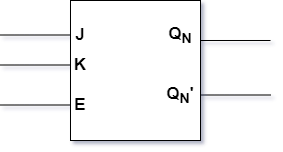

Block Diagram:

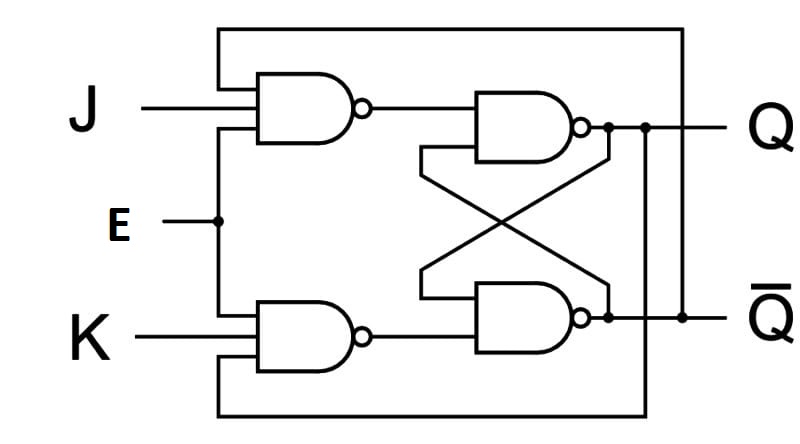

Circuit diagram:

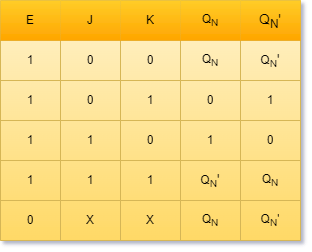

Truth table:

Working:

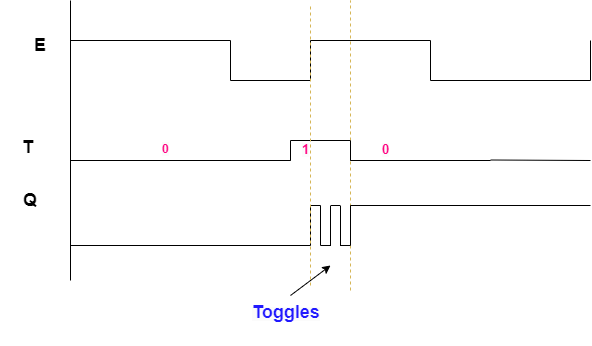

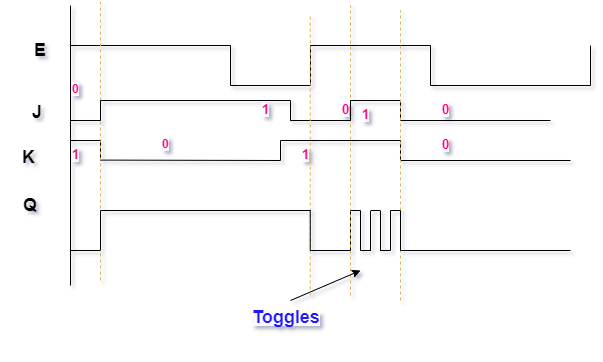

Timing diagram of Jk Latch

Gated T latch

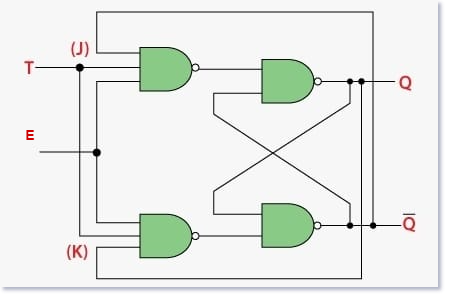

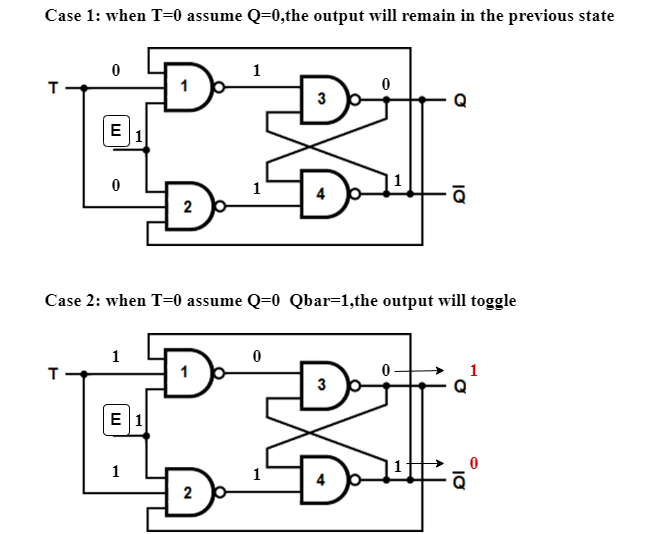

The JK latch inputs are shorted to create the T latch. The T latch’s output switches on and off when the input is set to 1 or high.When the input of T is 0 then the output will retain the same (no change).

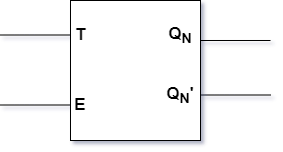

Block Diagram:

Circuit diagram:

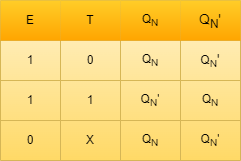

Truth table:

Working:

Timing Diagram: