Reconfiguring the LPC1768 Main PLL - tarasjg/mbed-vga GitHub Wiki

Time is of the essence

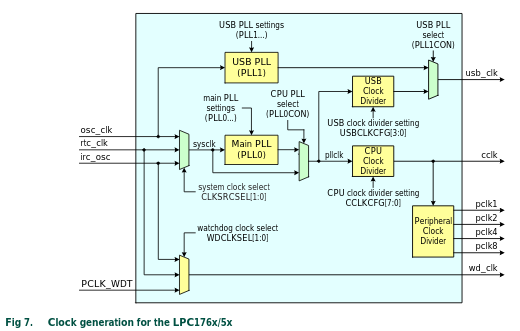

Out of the box, the LPC1768 has an internal clock speed of 96MHz (CCLK or PLL0). The peripheral clock divider of the LPC1768 only supports four configurations:

- 00 -> PCLK = CCLK/4

- 01 -> PCLK = CCLK

- 10 -> PCLK = CCLK/2

- 11 -> PCLK = CCLK/8

These bits, when written to a PCKLSELx register, define the peripheral clock. The I2S peripheral does not have a prescaler (some peripherals feature a 32 bit prescaler) but it must operate at ~25MHz. CCLK/4 out of the box is 24MHz, which won't work.

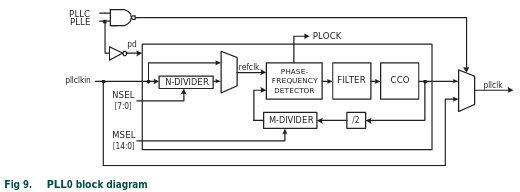

To remedy this, the main PLL (PLL0) is reconfigured to 100MHz. This is done by running a PLL initialization routine that reconfigures the N and M divider values of PLL0 to realign on 100MHz. PLL0 operation is shown in the figure below.

The N and M values were written to the PLL0 Control Register and the PLL0 Configuration Register, and asserted at each step using the PLL0 Feed Register. After the values were set, the routine waits for the read-only PLL0 Status Register to signal that the PLL has been substantiated and then connects the PLL0 to the system.

//assert PLL0CFG and PLL0CON regs

void main_pll_feed() {

__disable_irq();

LPC_SC -> PLL0FEED = 0x000000aa;

LPC_SC -> PLL0FEED = 0x00000055;

__enable_irq();

}

//set 100MHz chip pll

void init_main_pll() {

// the MBED crystal oscillator is 12 MHz

// main oscillator frequency 300 MHz: M = (300 x N) / (2 x 12)

int n = 2;

int m = 25;

// processor clock 100 MHz = 300 MHz / D

int d = 3;

// disconnect

LPC_SC -> PLL0CON = 0x00000001; main_pll_feed();

// disable

LPC_SC -> PLL0CON = 0x00000000; main_pll_feed();

// set new PLL values

LPC_SC -> PLL0CFG = ((n-1)<<16)|(m-1); main_pll_feed();

// enable

LPC_SC -> PLL0CON = 0x00000001; main_pll_feed();

// set cpu clock divider

LPC_SC -> CCLKCFG = (d-1);

// wait for lock

while (LPC_SC -> PLL0STAT&0x04000000==0);

// connect

LPC_SC -> PLL0CON = 0x00000003; main_pll_feed();

}

This clock initialization step permits a CCLK/4 of 25MHz, which aligns the I2S bitstream to the VGA specification. More details can be found in Chapter 4, Section 5 of the LPC1768 User Manual.