Pixel | LPC1768 DMA and I2S - tarasjg/mbed-vga GitHub Wiki

Pixel Data

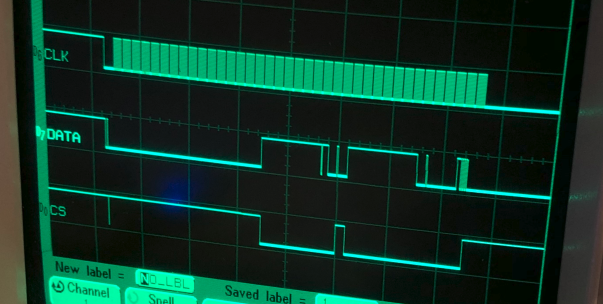

As touched on briefly, the SSPx peripherals of the LPC1768 were found not suitable to support a truly continuous bitstream. Formal documentation for the phenomenon was not found, but it was observed that a 1 cycle dead zone occurred between words - not only in data but in clock too. It is speculated that this is because the SSP does not have its own transmit buffer, thus requiring a 1 cycle load command to connect the next word to be transmitted to the peripheral. An example can be seen in the figure below, see the gaps in the CLK signal:

I2S, since it is designed for audio, is specifically designed to ensure continuity in the bitstream. At its heart, the I2S interface is driven by its FIFO controller. This buffer controller is highly configurable to word size and more importantly: trigger depth. The FIFO controller will trigger a DMA (or IRQ) request when the buffer is getting low. Interestingly, if the DMA cannot provide new data then the I2S interface will loop the current word. Perhaps this is what is happening when you get a 'skipping' effect on common cheap mp3 players?

The DMA controller is richly featured. It supports linked list control, which allows for a blanking sequence to be appended to the end of the each line. Further, it features a terminal count interrupt that triggers at the end of each linked list item. More clever VGA solutions utilize this to trigger not only for blanking but for HSYNC and VSYNC timer enable. In some places in memory, burst access is not permitted. To ensure continuity, the active window framebuffer is initialized in AHBx SRAM - addr 0x2009C000 on the LPC1768.

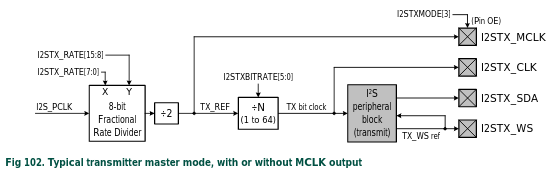

Transmit configuration for the I2S peripheral involves defining its operation mode along with its transmit clock. Transmitter master mode best suits this use case.

The I2S peripheral features a 8-bit fractional divider on the PCLK input to the system. The minimum division is by 2. This sets a theoretical max of a 50MHz bit clock.