FPGA Results - tarasjg/mbed-vga GitHub Wiki

Results

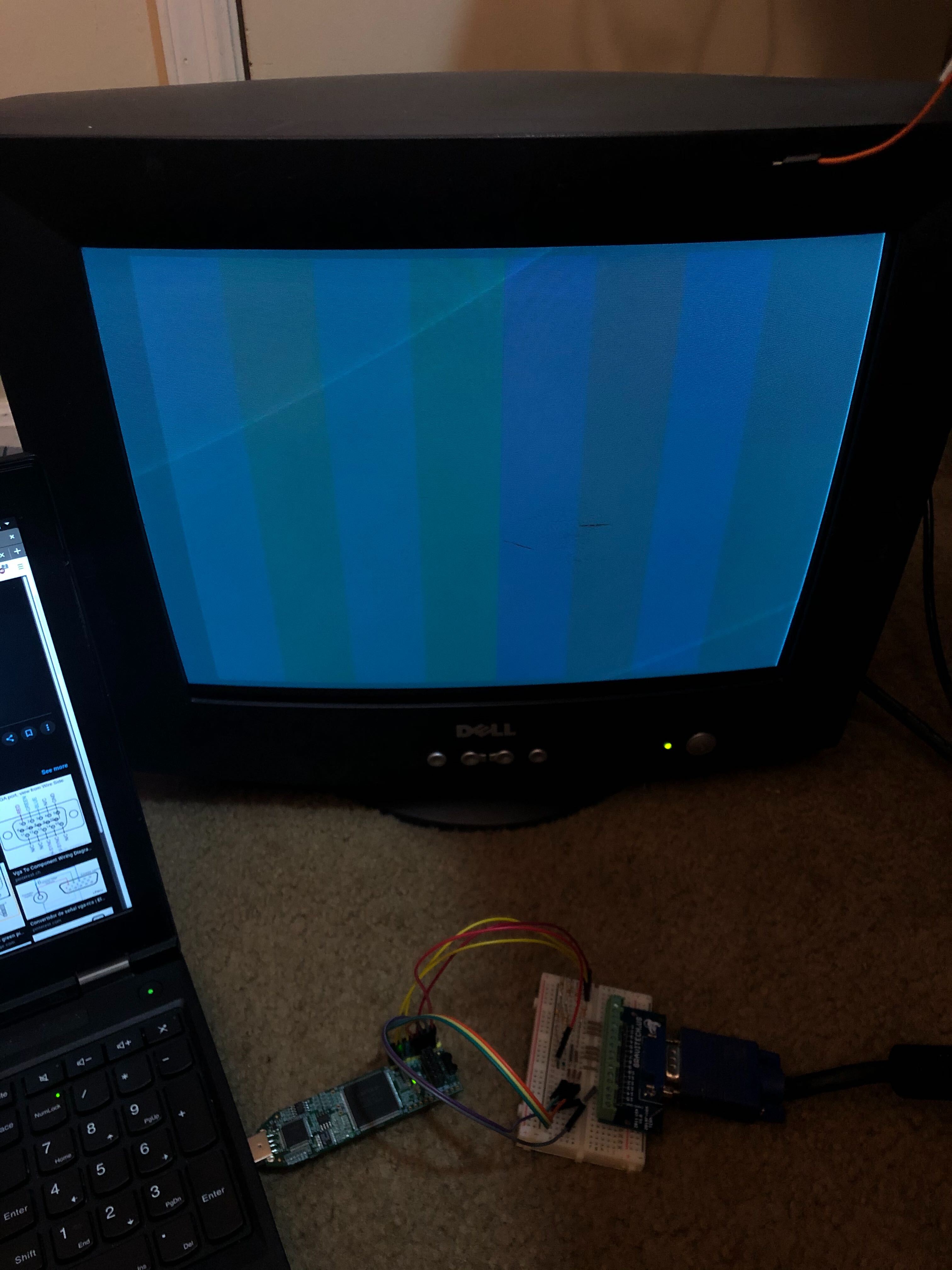

After implementation, a display routine was defined to cycle through different colors. Since this is an FPGA, it's more of a hardware definition rather than a routine. Headers were soldered to the iCE40 development board and connected to a VGA breakout board that was assembled:

Because there were limited resistors on hand, a simple resistor divider was used to drop the voltage down to the safe range of the pixel lines (0-0.7V). Due to lack of availability of proper driver end termination resistors (75 Ohm) along with significant loading from the cable, the brightness was low. Regardless, the script proved effective. An interesting thing to note is that because the FPGA provided much more accurate timing on HSYNC and VYSNC, the monitors recognized the target resolution.