Modulos - migarciapa/Electronica-Digital GitHub Wiki

Sumador

Este modulo es un sumador de dos números A y B cada uno con una longitud de 1 bit, el cual nos da como resultado un numero S de 1 bit, siendo S igual a la suma de las entradas, en caso de que la suma sea un número mayor a 1 para lo cual es necesario representarlo con mas de 1 bit existe un [Co] carry de salida.

Podemos observar en la siguiente tabla de verdad, como son las salidas S y Co a partir de las entradas A y B, ademas de una nueva entrada [Ci] carry de entrada, la cual es usada para la suma de números con mas de 1 bit de longitud.

Teniendo esto, podemos dibujar la caja negra de nuestro sumador completo de 1 bit, con 3 entradas A, B y Ci, y 2 salidas S y Co

Dentro de dicha caja se puede poner la siguiente configuración de compuertas lógicas a partir de la tabla de verdad.

Sumador_4B

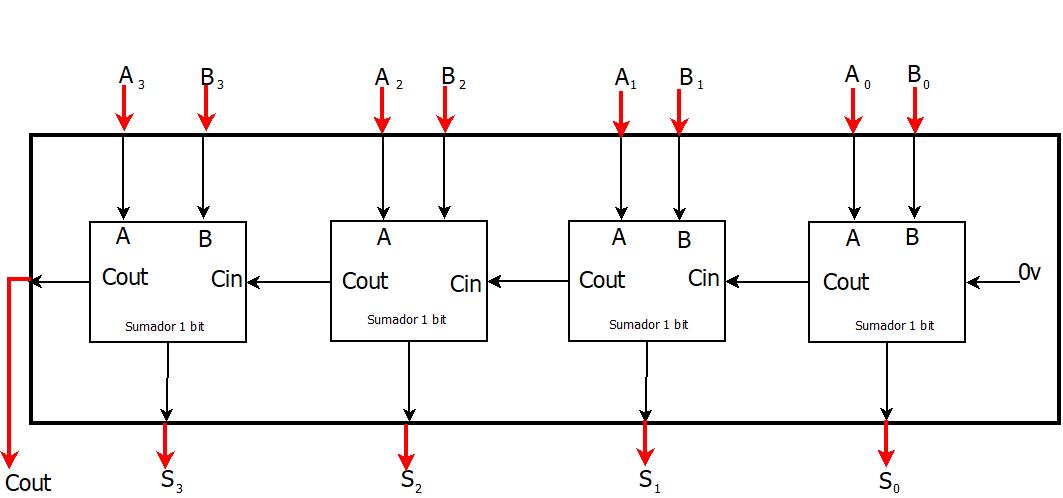

Haciendo uso de 4 sumadores de 1 bit del punto anterior se genera un modulo mas grande el cual tiene como entradas un numero A y uno B de 4 bits cada uno, donde el bit menos significativo esta asignado a la posición en la posición Ao y Bo, y el mas significativo esta en la A3 y B3, el Co del primer sumador de 1 bit sera el Ci del segundo y asi sucesivamente hasta que el Co del ultimo sumador de 1 bit sera el Co de todo el modulo. Con salidas S de 4 bits y Co de 1 bit.

A partir de lo anterior se puede hacer el dibujo de la caja negra, el cual queda de la siguiente manera:

Comparador

Este modulo consiste en poder comparar dos números A y B, para saber si A es mas mayor, menor o igual a B. Para ello podemos plantear una tabla de verdad la cual tenga de entradas A, B, GL y LL, con GL siendo una entrada que nos indica si la comparación del bit anterior es mas grande y LL si en la comparación anterior A es menor que B, como en este comparador solo se hace uso de dos números de 1 bit cada uno no son necesarias, pero a futuro si se usaran. Ademas tiene salidas G y L, estas nos indican si A es mayor o menor a B respectivamente.

Comparador_4B

Aquí al igual que en el sumador de 4 bits, reutilizamos el modulo anterior y construimos uno mas grande capaz de comparar dos números A y B de 4 bits cada uno, donde inicialmente compara el bit mas significativo de cada numero que estará en la posición A3 y B3, donde si uno es mayor o menor la salida es directamente ese resultado, en caso de ser iguales, se empieza a comparar el siguiente bit mas significativo hasta la posición Ao y Bo, si en ninguna de las comparaciones existe un bit que sea mas grande que el otro, entonces, se tiene una salida que nos indica si los números comparados son exactamente iguales.

Decodificador_7S

Este modulo se implementa para lograr la correcta visualización de un numero en un display de 7 segmentos, para lo cual se hace uso de una entrada X con una longitud de 4 bits, la cual nos permite representar del 0 al 15 en base hexadecimal, y una salida D de 7 bits que son los encargados de indicarle al display cuales leds necesita encender.

Para esto se plantea la siguiente tabla de verdad, donde a cada numero decimal se le asigna una salida D, podemos mostrar estas salidas con una serie de compuertas lógicas y lograr el comportamiento deseado e el circuito.

Multiplexor_4X1

Este modulo es la base para visualizar un número de mas de 2 cifras en dos displays distintos al mismo tiempo, ya que, nos permite controlar a partir de una señal de control/selección S, que valor mostrara la salida M, teniendo en cuenta que estara limitaada a los valores de entrada A, B, C o D, con esto podemos controlar que anodo de que display queremos ver encendido en un instante de tiempo t.

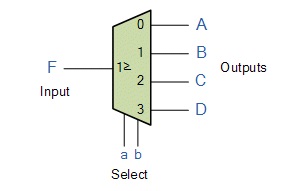

Demultiplexor_1X4

Este modulo es lo contrario a un multiplexor, ya que a partir de una entrada F y una señal de seleccion/control, decide en que salida A, B, C o D, se muestra la señal entrante.

Divisor_Frecuencia

Este modulo esta hecho principalmente para disminuir la velocidad de cambio que tiene la señal de reloj que viene por defecto en la FPGA, ya que tiene una frecuencia de unos 50 Mhz, para ello se usa una entrada Clk (reloj de la FPGA), y una salida Oclk, que tiene un valor de frecuencia deseado.

Contador_2B

Este modulo tiene la finalidad de ser la señal de control del multiplexor y demultiplexor, teniendo como entrada la señal de salida del divisor de frecuencia Oclk, y como salida un número C de 2 bits, que solo podra tener valores de 00, 01, 10 y 11.

Displayer_4_7S

En este modulo se hace una combinación de todos los módulos anteriores, ya que la finalidad de este bloque es lograr visualizar en varios displays la salida S de la suma de dos numeros A y B de 4 bits cada uno, en base hexadecimal, para lo cual es necesario usar el divisor de frecuencia junto con el multiplexor y contador, para lograr que se vea el resultado en varios displays "al mismo tiempo".

Decodificador_BCD_16B

Este modulo es un decodificador BCD de 16 bits de entrada [I], y 16 bits de salida [O], la cual se actualiza con cada borde positivo de un reloj de entrada [clk].

El BCD (Binary Coded Decimal) se trata de la escritura de un numero en formato binario, es decir a través de 0 o 1, en la que envés de que cada partición de el numero represente una potencia de 2, se toma de a escuadras, y cada cuatro posiciones se indica una potencia de diez, siendo la escuadra menos representativa las unidades, seguida de las decenas, centenas, unidades de mil, etc.

Por ejemplo, si queremos representar el numero 7598 en BCD, debe tomarse cada una de las cifras en base diez, llevarla a base dos, y luego concatenar, así:

7 -> 0111

5 -> 0101

9 -> 1001

8 -> 1000

BCD(7598) -> 0111010110011000

Sin embargo, para el decodificador BCD, se debe buscar una manera por la cual, se pueda generar el BCD teniendo solamente su código en binario, ya que la FPGA no es capaz de entender la base decimal.

Se decidió utilizar un algoritmo el cual se encuentra mas detalladamente explicado en el siguiente vídeo, y fue la fuente de nuestra consulta para crear el modulo:

https://www.youtube.com/watch?v=2JJxeKe5e5o

El algoritmo es relativamente sencillo. Se crea un registro con longitud suficiente para almacenar tanto nuestra entrada en binario, como nuestra salida en BCD.

El registro se inicia igualándose a la cantidad en binario. Leugo se le pide hacer una cantidad N de ciclos, donde N es la cantidad de bits que tiene nuestro binario. En cada ciclo se pide hacer lo siguiente:

- Verifique si alguna de los espacios escuadra del BCD es mayor o igual a 5. (Unidades>=5 ,Decenas>=5 ...)

- Si una escuadra cumple con la condicion anterior, sume 3 a la terna. ([Ej] Unidades=Unidades+3)

- Finalize desplazando el registro a la izquierda un espacio. (X=X*2)

En la siguiente tabla se puede ver el proceso de llevar el numero 156 (10011100) de binario a BCD, paso a paso: