AXI_SPI_Driver - jofranco/multi-rotor-on-FPGA GitHub Wiki

Overview

We used SPI communication protocol to talk with our Navigation Sensor. The SPI communication protocol requires one master and can support many slaves. In order to communicate with an external SPI sensor, we leveraged the Xilinx AXI Quad SPI, this provides us with an intermediary component to talk with the Navigation sensor without worrying about the AXI Lite interface used to move data around in the programmable logic of the FPGA. We built a custom driver that controls the Quad SPI through an SPI Bus which in turn allowed us to write/read to the Nav sensor. This is a custom driver that we developed.

Interface

This IP has an integer data type bus that is connected directly to the AXI Quad SPI. The bus is able to communicate with registers on the Quad SPI which are 32 bit addressable. The output of this core is an integer data type array of size 4032. The size of the array is the minimum address size setting for a HLS bundle.

Function

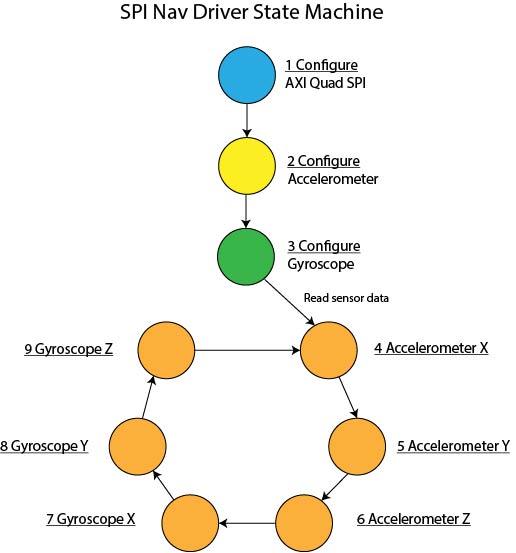

The overall function of this core is to grab raw data from the Nav Sensor and move it to another core that converted that raw data into useable data i.e. roll, pitch, and yaw with filtering to reduce noise. This core configures the AXI Quad SPI through the control register (SPICR) and allowed us to perform SPI transactions using the Quad SPI's SPI slave select register (SPISSR), SPI data transmit register (SPIDTR), SPI data receive register (SPIDRR). Leveraging the set of registers allowed us to communicate directly with the accelerometer and gyroscope like turning the accelerometer and gyroscope on/off, configuring precision of data measurements, and capturing measurements. In order to efficiently talk with the Nav sensor we created a State Machine to ensure the appropriate configuration sequence is set to determine validity of the data. The driver grabs 16 signed bits of data for accelerometer x,y,z and gyroscope x, y, z.

Additional Notes

Before arriving at this core, please ensure understanding of the AXI Quad SPI and most importantly the SPI communication protocol. Below is snapshot of the Vivado AXI Quad SPI settings that we used. In order to debug problems with the State Machine I also recommend using an oscilloscope to probe clock, Slave Select, MISO and MOSI data lines.