Interrupts - aryanjoshi0823/5143-Operating-System GitHub Wiki

Interrupts:

-

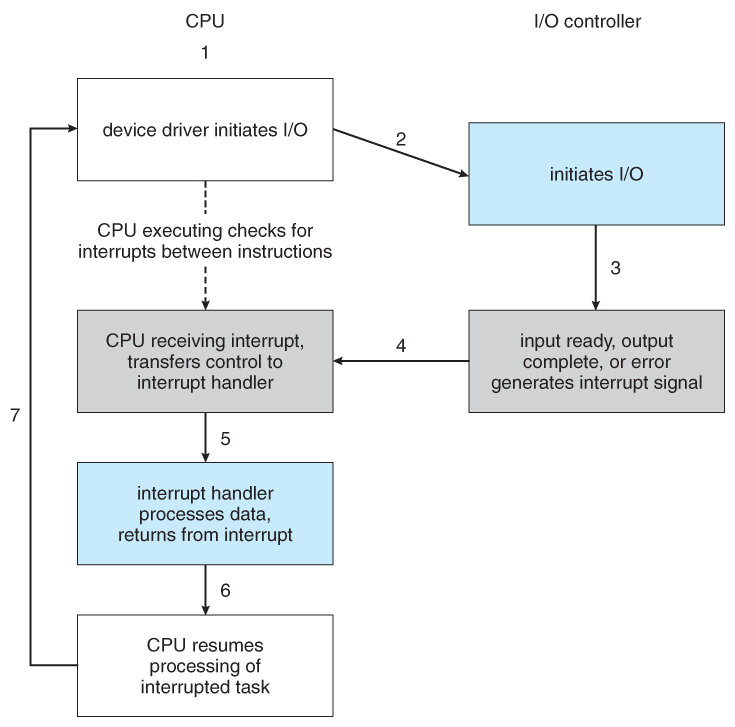

Interrupts allow devices to notify the CPU when they have data to transfer or when an operation is complete, allowing the CPU to perform other duties when no I/O transfers need its immediate attention.

-

The CPU has an interrupt-request line that is sensed after every instruction.

-

A device's controller raises an interrupt by asserting a signal on the interrupt request line.

-

The CPU then performs a state save, and transfers control to the interrupt handler routine at a fixed address in memory. ( The CPU catches the interrupt and dispatches the interrupt handler. )

-

The interrupt handler determines the cause of the interrupt, performs the necessary processing, performs a state restore, and executes a return from interrupt instruction to return control to the CPU. ( The interrupt handler clears the interrupt by servicing the device. )

-

Figure 13.3 illustrates the interrupt-driven I/O procedure:

The above description is adequate for simple interrupt-driven I/O, but there are three needs in modern computing which complicate the picture:

- The need to defer interrupt handling during critical processing,

- The need to determine which interrupt handler to invoke, without having to poll all devices to see which one needs attention, and

- The need for multi-level interrupts, so the system can differentiate between high- and low-priority interrupts for proper response.

Modern computer architectures use interrupt-controller hardware to manage interrupts effectively. Most CPUs have two interrupt-request lines: non-maskable for critical errors and maskable, which can be temporarily ignored during critical tasks.

-

Interrupts are mapped via an interrupt vector table, typically located at a fixed address, holding addresses of handlers for specific interrupts. Since the number of interrupt handlers often exceeds defined interrupt numbers, interrupt chaining is used, where vector addresses act as head pointers for linked lists of handlers.

-

For example, the Intel Pentium interrupt vector reserves interrupts 0–31 for non-maskable errors, while interrupts 32+ handle maskable tasks like I/O operations. Modern systems also support interrupt priorities, allowing high-priority interrupts to preempt lower-priority ones, ensuring efficient task handling.

-

At boot, the system identifies devices and loads their handler addresses into the interrupt table. During operation, interrupts signal events like errors, task completions, or exceptions (e.g., divide-by-zero or invalid memory access).

-

Interrupts enable multitasking through time slicing and context switching. A hardware timer triggers an interrupt, prompting the CPU to save the current state, run the scheduler, and restore the state of a different process. Virtual memory uses interrupts to handle page faults, moving processes between queues and resuming them after I/O completion.

-

System calls (software interrupts) allow user programs to request kernel services. These interrupts are low-priority compared to device interrupts, which may include: High-priority interrupts to issue new hardware requests, Low-priority interrupts to transfer data and update process queues.

-

Multi-threaded kernels like Solaris use priority threads to handle multiple interrupts simultaneously, ensuring high-priority tasks preempt low-priority ones and user processes for optimized performance.