ADC characterization - WCP52/docs GitHub Wiki

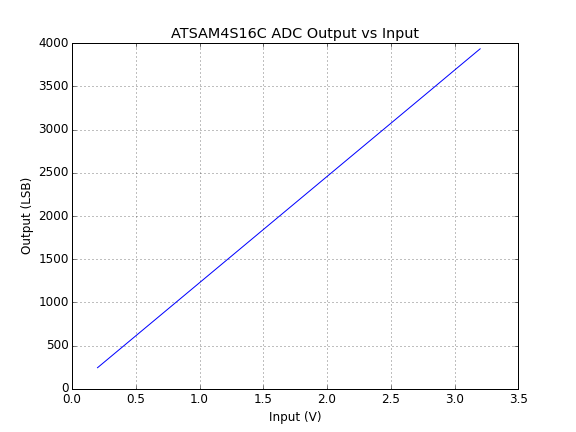

In order to quickly evaluate whether the A-D converter on the ATSAM4S16C is sufficient to collect data in our system, we took a simple measurement of its INL [1]. To do this, we used a very stable and precise voltage source (a Power Designs 2020 precision power supply) to step through the full input range in 200 mV increments, recording the raw output returned by the converter. A PyLab script was used to process the data, generating plots and a final computation.

| [1] | Integral nonlinearity: the worst-case difference between the reading returned by the converter and the reading which ''should'' have been returned by the converter. |

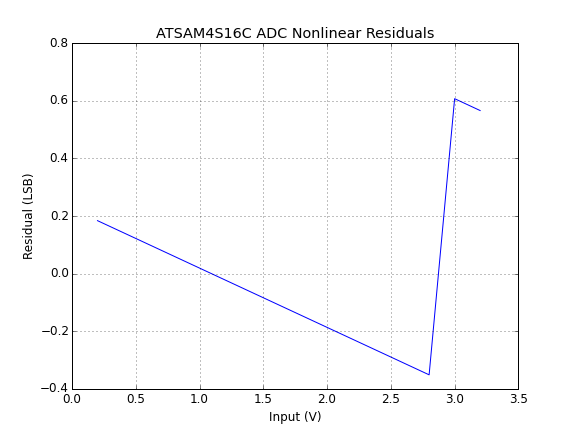

To compute INL, a linear fit is found for the input-vs-output curve, and then residuals are computed by subtracting the linear fit (the ''ideal'' input-vs-output curve) from the actual curve. The INL is simply the data point in this set with the largest magnitude.

The worst-case INL for our test was approximately 0.61 ''LSB'' (Least Significant Bits - the smallest increment of the ADC output value). Scaled to a 3.3V reference point (0.61 (3.3 / 4095)), this gives a 490 µV nonlinearity error, which corresponds to 20 mdB assuming we use the AD8310 logarithmic amplifier. This is a negligible error.