PWM - Kasimashi/Systemes-embarques GitHub Wiki

Pulse width modulation(PWM) est une technique numérique pour controler la valeur du variable analogique. Les PWM utilisent des signaux rectangulaire pour rapidement évoluer au niveau du voltage. En l'activant et déactivant rapidement on peut ainsi modifier la valeur moyenne lue et obtenir une autre valeur de voltage en sortie. Bien que la sortie soit à 5V ou à 0V de base, la moyenne sur un temps donné peut se trouver entre les deux.

Spécifiquement, le pourcentage de temps passé dans un état est proportionnel à la valeur moyenne de la sortie en volt. Par conséquent, quand le software change les durées des états, l'output voltage peut être utilisé pour emuler un signal analogique.

Les PWM sont très utilisé dans les applications, particulièrement pour contrôler la vitesse d'un moteur et pour la mesure du couple, pour l'encodement digital et les télécommunications, les convertisseurs DC vers DC, les amplificateurs audios. Dans cette section nous allons utiliser le PWM pour controler l'intensité d'une LED.

Nous devons sélectionner la variation de fréquence PWM minutieusement afin d'éviter les impacts sur les applications. Par exemple le changement de fréquence sur l'intensité d'une LED doit être inférieur à 120 Hz pour éviter l'effet vacillant pour que un humain puisse le voir.

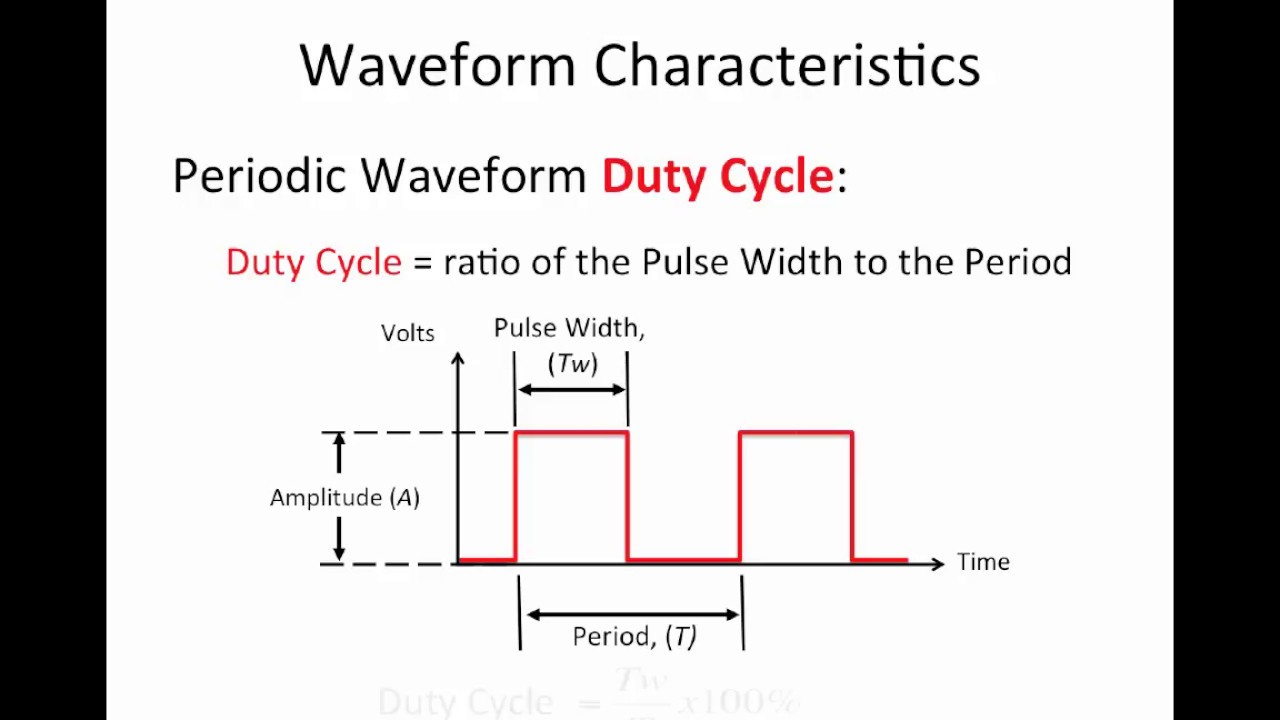

La valeur moyenne d'un PWM est basé sur un signal à dent de scie et une valeur constante de référence, tout ceci est linéairement proportionnel au duty cycle.

Le temps de cycle (duty cycle) est défini ainsi :

Ou

En modifiant le duty cycle, le software peut controler la valeur moyenne. Dans l'exemple de la LED la luminosité est déterminé par le PWM duty cycle.

Le signal PWM de sortie dépend de 3 facteurs :

- La comparaison entre le registre CNT et la valeur de référence donné dans le compare and capture register (CCR).

- Le mode PWM output mode

- Le bit de polarité

Il y a 2 modes PWM qui sont opposé l'un l'autre :

- PWM Mode 1: Si le compteur est plus petit que la référence, le timer reference output (OCREF) est dans un état haut. Sinon dans un état bas.

- PWM Mode 2: Si le compteur est plus grand que la référence, le timer reference output (OCREF) est dans un état haut. Sinon dans un état bas.

OCREF est une sortie interne. Qui doit toujours utiliser une logique d'état haut. Cependant la sortie actuelle (OC ou OCN) peut être active high ou active low.

- Dans le mode active high, un haut voltage corrrespond à une logique haute, et un bas voltage à une logique basse.

- Dans le mode active low, un haut voltage correspond à une logique basse, et un bas voltage à une logique haute.

- La selection de ce mode se fait via le bit de polarité.

Pour résumé, la sortie PWM(OC ou OCN) est obtenue par le mode et le bit de polarité. Les formules suivantes permettent de calculer la période du PWM :

Pour un mode upcounting ou downcounting :

Pour un mode center-counting-mode :

Pour le PWM duty cycle, suivant le mode du PWM et le bit de polarité, le duty cycle de la sortie principale OC en mode upcounting ou downcounting est :

ou de son complémentaire

Pour le mode center-counting on a :

ou de son complémentaire

Dans le mode center aligned , quand le registre CCR est à 0 ou le registre ARR, OCREF est 1 ou 0. Cela dépend du mode PWM.

"Toutes les sorties PWM d'un même timer ont les mêmes périodes"

Un timer possède plusieurs canaux comme vue plus haut. Tout les canaux partagent le même timer counter et le registre ARR. Ainsi, tout les signaux PWM produit par le même timer ont les mêmes périodes. Cependant leurs duty cycles peuvent être différent car chaques canaux a un CCR différent.