wiki - KS10FPGA/KS10FPGA GitHub Wiki

The KS10 FPGA Project

Copyright 2023

Rob Doyle

doyle (at) cox (dot) net

1 The KS10 FPGA Project

1.1 Project Goals

1.2 The DEC KS10

1.3 The KS10 FPGA

1.4 KS10 FPGA Status

1.5 DEC KS10 Documentation

2 The Host Computer System

2.1 Cloning the KS10 FPGA Github Repository

2.2 The Installation Tree

2.3 Building the Console Processor Executable

2.3.1 Cygwin Software Build

2.3.2 Windows Subsystem for Linux (WSL) Software Build

2.3.3 On Target Software Build

2.4 FPGA Firmware Tooling

2.4.1 Quartus 18.1 for Windows FPGA Firmware Build Process

2.4.2 Quartus 21.1 for Windows FPGA Firmware Build Process

2.4.3 Quartus 21.1 for Linux/WSL FPGA Firmware Build Process

2.5 Building the FPGA Firmware

2.5.1 FPGA Firmware Build Rules

2.6 Building the Custom KS10 Development Tools

2.6.1 asm10

2.6.2 tapeutils

2.6.3 sav2verilog

2.6.4 Merge18 and merge36

2.7 Co-simulating the FPGA RTL and PDP-10 Software

2.7.1 Simulating with ModelSim

2.7.1.1 ModelSim Limitations

2.7.2 Simulating with QuestaSim

2.7.3 Simulation using Icarus Verilog

2.7.4 Co-simulating FPGA and PDP-10 Software

2.7.5 Extracting the RED PACK from Magtape

2.8 Extracting the KS10 Diagnostics from Magtape

2.9 Initializing the RP06 Disk Drives

2.9.1 Background

2.9.2 Disk Partitioning

2.9.3 Disk Formatting

2.9.4 Cygwin Programming Procedure

2.9.4.1 Step 1: Select the disk device

2.9.4.2 Step 2: Programming the selected disk device

2.9.5 WSL Programming Procedure

2.9.6 Linux Programming Procedure

3 Console Processor

3.1 Status

4 Console Hardware

4.1 Target Hardware

4.1.1 DE10-NANO Development Kit

4.1.2 Intel Cyclone 5 System on a Chip

4.1.3 KS10 FPGA Daughter Board

4.1.4 USB Hub

4.2 Schematic and PWB Layout Design Information

4.3 My Target Configuration

4.3.1 WiFi

4.4 Other Issues that needed to be solved.

4.5 Hardware Status

5 BUS: KS10 Backplane Bus Cycles

5.1 BUS: KS10 Address Bus

5.2 BUS: KS10 Data Bus

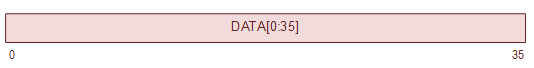

5.2.1 BUS: KS10 Bus Cycles

5.2.2 BUS: KS10 Memory Read and Write Cycles

5.2.2.1 BUS: KS10 Memory Read Cycle

5.2.2.2 BUS: KS10 Memory Write Cycle

5.2.3 BUS: KS10 IO Read and Write Cycle

5.2.3.1 BUS: KS10 Word IO Read Cycle (36-bit or 16-bit)

5.2.3.2 BUS: KS10 Byte IO Read Cycle

5.2.3.3 BUS: KS10 Word IO Write Cycle (36-bit or 16-bit)

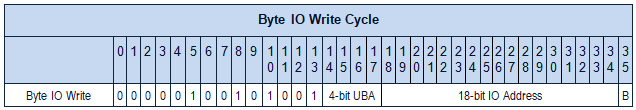

5.2.3.4 BUS: KS10 Byte IO Write Cycle

5.2.4 BUS: KS10 Who Are You (WRU) Cycle

5.2.5 BUS: KS10 Interrupt Vector Cycle

5.3 BUS: KS10 Interrupt Sequence

6 CON: KS10 Console Interface

6.1 CON: KS10 Interface Register Set

6.1.1 CON: KS10 Console Address Register (CONAR)

6.1.2 CON: KS10 Console Data Register (CONDR)

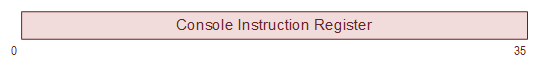

6.1.3 CON: KS10 Console Instruction Register (CONIR)

6.1.4 CON: KS10 Console Control/Status Register (CONCSR)

6.1.5 CON: DZ11 Console Control Register (DZCCR)

6.1.6 CON: LP20 Console Control Register (LPCCR)

6.1.7 CON: Magtape Console Control Register (MTCCR)

6.1.8 CON: RP Console Control Register (RPCCR)

6.1.9 CON: DUP11 Console Control Register (DUPCCR)

6.1.10 CON: KMC11 Control Register (KMCCCR)

6.1.11 CON: KS10 Breakpoint Address Registers (BRAR[0:3])

6.1.12 CON: KS10 Breakpoint Mask Registers (BRMR[0:3])

6.1.13 CON: KS10 Instruction Trace Register (ITR)

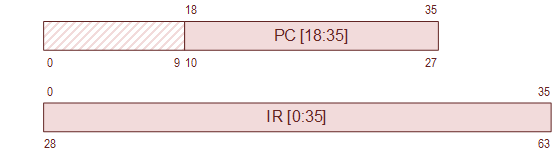

6.1.14 CON: PC and IR (PCIR) Registers

6.1.15 CON: MT Data Interface Register (MTDIR)

6.1.16 CON: MT Debug Register (MTDEBUG)

6.1.17 CON: RP Debug Register (RPDEBUG)

6.1.18 CON: KS10 Firmware Version Register (FVR)

6.2 CON: KS10 Control Interface

6.2.1 CON: The RUN bit

6.2.2 CON: The CONT bit

6.2.3 CON: The EXEC bit

6.3 CON: KS10 Console Communications Area

6.3.1 CON: KS10 Halt Switch

6.3.2 CON: KS10 Keep Alive Word

6.3.3 CON: KS10 CTY Input Word

6.3.4 CON: KS10 CTY Output Word

6.3.5 CON: KS10 KLINIK Input Word

6.3.6 CON: KS10 KLINIK Output Word

6.3.7 CON: KS10 Boot RH11 Address

6.3.8 CON: KS10 Boot Unit Number

6.3.9 CON: Magtape Parameters

6.4 CON: Console Status

7 KS10: The KS10 FPGA Block Diagram

8 CPU: The KS10 CPU

8.1 CPU: Functional Blocks

8.1.1 CPU: Arithmetic Logic Unit (ALU)

8.1.2 CPU: Arithmetic Processor Flags (APR)

8.1.3 CPU: Backplane Bus Interface (BUS)

8.1.4 CPU: DBM Multiplexer (DBM)

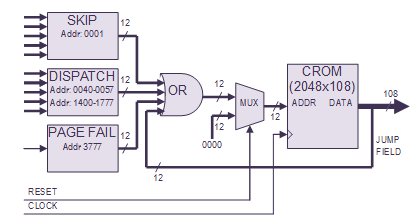

8.1.5 CPU: DBUS Multiplexer (DBUS)

8.1.6 CPU: Byte Dispatch (DISP_BYTE)

8.1.7 CPU: Next Instruction Dispatch (DISP_NI)

8.1.8 CPU: Page Fail / Interrupt Dispatch (DISP_PF)

8.1.9 CPU: Console Interface (INTF)

8.1.10 CPU: Microsequencer (USEQ)

8.1.10.1 CPU: Microsequencer Dispatch (DISPATCH)

8.1.10.2 CPU: Microsequencer Skip (SKIP)

8.1.10.3 CPU: Microsequencer Stack (STACK)

8.1.10.4 CPU: Microsequencer Control ROM (CROM)

8.1.10.5 CPU: Microsequencer Dispatch ROM (DROM)

8.1.11 CPU: Non-existent Device (NXD)

8.1.12 CPU: Non-existent Memory (NXM)

8.1.13 CPU: Pager (PAGER)

8.1.14 CPU: PC Flags (PCFLAGS)

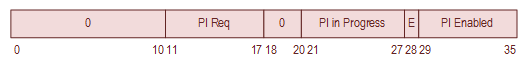

8.1.15 CPU: Priority Interrupt (PI)

8.1.16 CPU: Previous Context (PXCT)

8.1.17 CPU: KS10 RAM File (RAMFILE)

8.1.18 CPU: Instruction Register (IR)

8.1.19 CPU: Step Count Adder (SCAD)

8.1.20 CPU: Interval Timer (TIMER)

8.2 CPU: Performance / DSKFAA0 Benchmark Summary

8.3 CPU: Status

9 MEM: DEC KS10 Memory Controller

9.1 MEM: ADP Modifications to Memory Controller

9.2 MEM: Memory Controller Register Set

9.2.1 MEM: Memory Status Register (MSR)

9.3 MEM: SSRAM Memory Interface

9.3.1 MEM: x18-bit SSRAM Interface

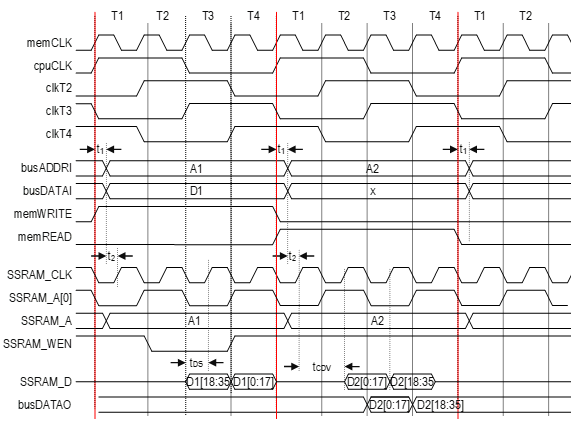

9.3.1.1 MEM: SSRAM Read and Write Cycles

9.3.1.1.1 MEM: SSRAM Read Cycle

9.3.1.2 MEM: SSRAM Write Cycle

9.3.2 MEM: 36-bit SSRAM Interface

9.3.2.1 MEM: SSRAM Read Cycle

9.3.2.2 MEM: SSRAM Write Cycle

9.4 MEM: Status

10 UBA: IO Bus Bridge

10.1 UBA: Register Set

10.1.1 UBA: Status Register (UBASR)

10.1.2 UBA: Maintenance Register (UBAMR)

10.2 UBA: Address Translation (Paging)

10.2.1 UBA: Paging Memory (UBAPAG)

10.2.2 UBA: Page Failure

10.3 UBA: IO Data Translation

10.4 UBA: DSUBA Transcripts

10.4.1 UBA: DSUBA Transcript With No UBEs Attached

10.4.2 UBA: DSUBA Transcript With UBEs Attached

10.5 UBA: Status

11 RH: Massbus Controller

11.1 RH: Register Set Summary

11.2 RH: Massbus Register Set

11.2.1 RH: Control and Status #1 (RHCS1) Register

11.2.2 RH: Word Count (RHWC) Register

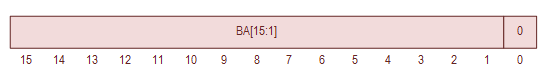

11.2.3 RH: Bus Address (RHBA) Register

11.2.4 RH: Control and Status #2 (RHCS2) Register

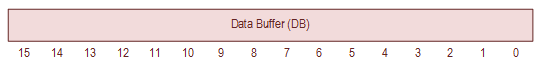

11.2.5 RH: Data Buffer (RHDB) Register

11.3 RH: Interrupts

11.4 RH: Status

12 RP: Massbus Disk Controller (RP)

12.1 RP: Massbus Disk Controller Implementation

12.2 RP: Disk Parameters

12.3 RP: Compatibility between Massbus Disk Drives and the SD Card

12.3.1 RP: Sector Size

12.3.2 RP: Sector Addressing

12.3.3 RP: Data Transfer Rates

12.3.4 RP: Seek time and Search Time

12.3.5 RP: Partial Reads and Writes

12.3.6 RP: The RP06 Disk in Detail

12.4 RP: Device Registers Summary

12.5 RP: Register Set

12.5.1 RP: Control and Status #1 Register (RPCS1)

12.5.2 RP: Disk Address Register (RPDA)

12.5.3 RP: Drive Status Register (RPDS)

12.5.4 RP: Error #1 Register (RPER1)

12.5.5 RP: Attention Summary Register (RPAS)

12.5.6 RP: Look Ahead Register (RPLA)

12.5.7 RP: Maintenance Register (RPMR)

12.5.8 RP: Drive Type Register (RPDT)

12.5.9 RP: Serial Number Register (RPSN)

12.5.10 RP: Offset Register (RPOF)

12.5.11 RP: Desired Cylinder Register (RPDC)

12.5.12 RP: Current Cylinder Register (RPCC)

12.5.13 RP: Error Status #2 Register (RPER2)

12.5.14 RP: Error Status #3 Register (RPER3)

12.5.15 RP: Error Position Register (RPEC1)

12.5.16 RP: Error Pattern Register (RPEC2)

12.6 RP: Functions

12.7 RP: Status

12.8 RP: Emulated Disk Benchmarks

13 MT: Massbus Tape Controller (MT)

13.1 MT: Device Registers Summary

13.2 MT: Register Set

13.2.1 MT: Control and Status #1 Register (MTCS1)

13.2.2 MT: Frame Count Register (MTFC)

13.2.3 MT: Drive Status Register (MTDS)

13.2.4 MT: Error Register (MTER)

13.2.5 MT: Attention Summary Register (MTAS)

13.2.6 MT: Character Check Register (MTCC)

13.2.7 MT: Maintenance Register (MTMR)

13.2.8 MT: Drive Type Register (MTDT)

13.2.9 MT: Serial Number Register (MTSN)

13.2.10 MT: Tape Control Register (MTTC)

13.3 MT: Functions

13.4 MT: Data Interface Register (MTDIR)

13.5 MT: Timing Parameters

13.6 MT: Console Processor Software

13.6.1 MT: Beginning of Tape (BOT)

13.6.2 MT: End of Tape (EOT)

13.7 MT: Tape Formatting

13.7.1 MT: Tape Format: PDP-10 Core Dump Format

13.7.2 MT: Tape Format: PDP-10 Seven Track Format

13.7.3 MT: Tape Format: PDP-10 ASCII Format

13.7.4 MT: Tape Format: PDP-10 Compatible Format

13.7.5 MT: Tape Format: PDP-11 Normal Tape Format

13.7.6 MT: Tape Format: PDP-15 Normal Tape

13.8 MT: RH11/TM03/TU45 Status

13.8.1 MT: Diagnostic Transcripts

13.8.1.1 MT: DSTUA Basic Device Diagnostic Results

13.8.1.2 MT: DSTUB Reliability Diagnostic Results

13.8.2 MT: Status

14 DZ: Terminal Multiplexer

14.1 DZ: DZ11 Register Set

14.1.1 DZ: Control and Status Register (DZCSR)

14.1.2 DZ: Receiver Buffer Register (DZRBUF)

14.1.3 DZ: Line Parameter Register (DZLPR)

14.1.4 DZ: Transmit Control Register (DZTCR)

14.1.5 DZ: Modem Status Register (DZMSR)

14.1.6 DZ: Transmit Data Register (DZTDR)

14.2 DZ: Interrupts

14.2.1 DZ: Transmitter Interrupt

14.2.2 DZ: Receiver Interrupt

14.3 DZ: Status

15 LP: LP20 Printer Controller

15.1 LP: LP20 Registers

15.1.1 LP: Control/Status A Register (LPCSRA)

15.1.2 LP: Control/Status B Register (LPCSRB)

15.1.3 LP: Bus Address Register (LPBAR)

15.1.4 LP: Byte Count Register (LPBCTR)

15.1.5 LP: Page Count Register (LPPCTR)

15.1.6 LP: RAM Data Register (LPRAMD)

15.1.7 LP: Column Counter Register (LPCCTR) / Character Buffer Register (LPCBUF)

15.1.8 LP: Checksum Register (LPCKSM) / Printer Data Register (LPPDAT)

15.2 LP: Interrupts

15.3 LP: Modes

15.3.1 LP: Print Mode

15.3.2 LP: Test Mode

15.3.3 LP: Normal Test Mode

15.3.4 LP: Demand Timeout Test Mode

15.3.5 LP: SSYN Timeout Test Mode

15.3.6 LP: RAM Parity Test Mode

15.3.7 LP: Memory Parity Test Mode

15.3.8 LP: Line Printer Parity Test Mode

15.3.9 LP: Page Counter Test Mode

15.3.10 LP: Load DAVFU Mode

15.3.11 LP: Load Translation RAM Mode

15.4 LP: DSLPA Transcript

15.5 LP: FPGA Status

16 LP: LP26 Printer

16.1 LP: LP26 Characteristics

16.2 LP: LP26 Vertical Format Units

16.2.1 LP: LP26 Tape Controlled Vertical Format Unit (TCVFU)

16.2.2 LP: LP26 Direct Access Vertical Format Unit (DAVFU)

16.2.2.1 LP: LP26 DAVFU Loading

16.2.2.1.1 LP: LP26 DAVFU Start Load Codes

16.2.2.1.2 LP: LP26 DAVFU Stop Load Codes

16.2.2.2 LP: LP26 DAVFU Use

16.2.2.2.1 LP: LP26 DAVFU Absolute Motion (Channel Codes)

16.2.2.2.2 LP: LP26 DAVFU Relative Motion (Slew)

16.2.3 LP: LP26 Error Conditions

17 DUP: DUP11 Synchronous Serial Interface

17.1 DUP: Synchronous Serial Protocols

17.1.1 DUP: SDLC/ADCCP Protocol

17.1.2 DUP: DDCMP/BISYNC Protocol

17.2 DUP: DUP11 Registers

17.2.1 DUP: Receiver Control/Status Register (RXCSR)

17.2.2 DUP: Received Data Buffer (RXDBUF)

17.2.3 DUP: Parameter Control/Status Register (PARCSR)

17.2.4 DUP: Transmitter Control/Status Register (TXCSR)

17.2.5 DUP: Transmitter Data Buffer (TXDBUF)

17.3 DUP: Interrupts

17.3.1 DUP: Receiver Interrupt

17.3.2 DUP: Transmitter Interrupt

17.4 DUP: DSDUA Transcript

17.5 DUP: FPGA Status

18 KMC: KMC11 Microprocessor

18.1 KMC: KMC11 Register Summary

18.1.1 KMC: Control and Status Registers

18.1.2 KMC: Maintenance Register

18.1.3 KMC: Maintenance Address Register

18.1.4 KMC: Maintenance Instruction Register

18.2 KMC: Microprocessor Registers

18.2.1 KMC: NPR Input Data (NPRID) Register

18.2.2 KMC: NPR Output Data (NPROD) Register

18.2.3 KMC: NPR Input Address (NPRIA) Register

18.2.4 KMC: NPR Output Address (NPROA) Register

18.2.5 KMC: CSR0 Register

18.2.6 KMC: CSR1 Register

18.2.7 KMC: CSR2 Register

18.2.8 KMC: CSR3 Register

18.2.9 KMC: CSR4 Register

18.2.10 KMC: CSR5 Register

18.2.11 KMC: CSR6 Register

18.2.12 KMC: CSR7 Register

18.2.13 KMC: NPR Control Register (KMCNPRC)

18.2.14 KMC: MISC Register (KMCMISC)

18.3 KMC: DSKMA Transcript

18.4 KMC: Status

19 UBE: Unibus Adapter Exerciser

19.1 UBE: Interface Registers

19.1.1 UBE: Data Buffer Register (UBEDB)

19.1.2 UBE: Cycle Count Register (UBECC)

19.1.3 UBE: Buffer Address Register (UBEBA)

19.1.4 UBE: Control/Status Register #1 (UBECSR1)

19.1.5 UBE: Clear Error Register (UBECLR)

19.1.6 UBE: Control/Status Register #2 (UBECSR2)

19.1.7 UBE: Simultaneous GO Register (SIMGO)

19.2 UBE: DSUBA Transcript

19.3 UBE: Status

20 DSKFAA0 Benchmark Summary

21 Creating the REDPACK

22 Exploring the REDPACK

23 Building the Microcode

Figure 1 - The DEC KS10

Figure 2 - The DEC KS10 with Covers Removed

Figure 3 - KS10 FPGA in Mini-ITX chassis

Figure 4 - KS10 FPGA Block Diagram

Figure 5 - KS10 FPGA design on Intel Cyclone 5 System on Chip (SoC)

Figure 6 - KS10 FPGA Hardware (Side View)

Figure 7 - KS10 FPGA Hardware (Front View)

Figure 8 - KS10 FPGA Hardware Configuration

Figure 9 - BUS: KS10 FPGA Block Diagram

Figure 10 - BUS: KS10 Address Bus Definition

Figure 11 - BUS: KS10 Memory Read Cycle

Figure 12 - BUS: KS10 Memory Write Cycle

Figure 13 - BUS: KS10 Word IO Read Cycle

Figure 14 - BUS: KS10 Byte IO Read Cycle

Figure 15 - BUS: KS10 Word IO Write Cycle

Figure 16 - BUS: KS10 Byte IO Write Cycle

Figure 17 - BUS: KS10 WRU Cycle

Figure 18 - BUS: KS10 Interrupt Vector Cycle

Figure 19 - CON: KS10 Console Address Register (CONAR)

Figure 20 - CON: KS10 Console Address Register (CONAR) Bit Definitions

Figure 21 - CON: KS10 Console Data Register (CONDR)

Figure 22 - CON: KS10 Console Instruction Register (CONIR)

Figure 23 - CON: KS10 Console Control/Status Register (CONCSR)

Figure 24 - CON: DZ11 Console Control Register (DZCCR)

Figure 25 - CON: LP Console Control Register (LPCCR)

Figure 26 - CON: MT Console Control Register (MTCCR)

Figure 27 - CON: RP Console Control Register (RPCCR)

Figure 28 - CON: DUP11 Console Control Register (DUPCCR)

Figure 29 - CON: KS10 Breakpoint Address Register (BRAR[0:3])

Figure 30 - CON: KS10 Breakpoint Mask Register (BRMR[0:3])

Figure 31 - CON: KS10 Instruction Trace Register (ITR)

Figure 32 - CON: KS10 Program Counter and Instruction Register (PCIR)

Figure 33 - CON: MT Debug Register (MTDEBUG)

Figure 34 - CON: RP Debug Register (RPDEBUG)

Figure 35 - CON: KS10 Firmware Version Register (FVR)

Figure 36 - CON: KS10 Control State Diagram

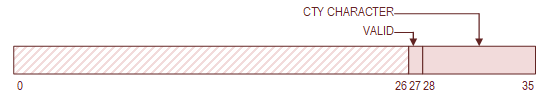

Figure 37 - CON: KS10 CTY Input Word (KS10 Memory Address 000032)

Figure 38 - CON: KS10 CTY Output Word (KS10 Memory Address 000033)

Figure 39 - KS10: FPGA Block Diagram

Figure 40 - CPU: Block Diagram

Figure 41 - CPU: ALU Implementation (DEC KS10)

Figure 42 - CPU: ALU Implementation (KS10 FPGA)

Figure 43 - CPU: Extended Addressing

Figure 44 - CPU: Physical Addressing

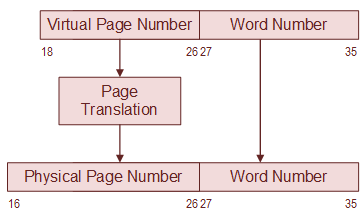

Figure 45 - CPU: Paged Addressing

Figure 46 - CPU: WRU Addressing

Figure 47 - CPU: Bus Interface Block Diagram

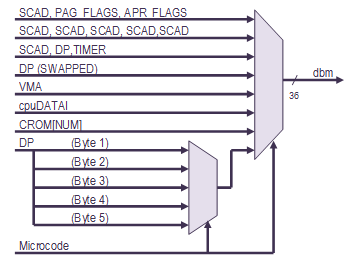

Figure 48 - CPU: DBM Block Diagram

Figure 49 - CPU: DBUS Block Diagram

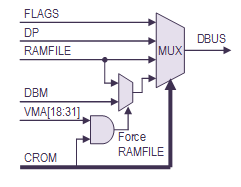

Figure 50 - CPU: Microsequencer Block Diagram

Figure 51 - CPU: Microseqencer Stack

Figure 52 - CPU: Pager Address Translation

Figure 53 - CPU: Pager Block Diagram

Figure 54 - CPU: Priority Interrupt Register

Figure 55 - CPU: Priority Interrupt Block Diagram

Figure 56 - CPU: SCAD Block Diagram

Figure 57 - CPU: Interval Timer Register

Figure 58 - CPU: Interval Timer Block Diagram

Figure 59 - MEM: Memory Status Register (Read)

Figure 60 - MEM: Memory Status Register (Write)

Figure 61 - MEM: Burst Mode SSRAM Address and Data Mapping

Figure 62 - MEM: SSRAM Write Cycle followed by and Read Cycle

Figure 63 - MEM: SSRAM Read Cycle

Figure 64 - MEM: SSRAM Read Cycle Timing Parameters

Figure 65 - MEM: SSRAM Write Cycle

Figure 66 - MEM: SSRAM Write Cycle Timing Parameters

Figure 67 - UBA: Status Register (UBASR)

Figure 68 - UBA: Maintenance Register (UBAMR)

Figure 69 - UBA: Address Translation (Paging)

Figure 70 - UBA: Paging RAM (Write)

Figure 71 - UBA: Paging RAM (Read)

Figure 72 - UBA: Byte and Word Translation into a 36-bit Word

Figure 73 - RH: Control and Status #1 Register (RHCS1)

Figure 74 - RH: Word Count Register (RHWC)

Figure 75 - RH: Bus Address Register (RPBA)

Figure 76 - RH: Control and Status Register #2 (RHCS2)

Figure 77 - RH: Data Buffer Register (RPDB)

Figure 78 - RP: Massbus Disk Controller Block Diagram

Figure 79 - RP: Massbus Disk Addressing

Figure 80 - RP: Control and Status Register #1 (RPCS1)

Figure 81 - RP: Disk Address Register (RPDA)

Figure 82 - RP: Drive Status Register (RPDS)

Figure 83 - RP: Error Register #1 (RPER1)

Figure 84 - RP: Attention Summary Register (RPAS)

Figure 85 - RP: Look Ahead Register (RPLA)

Figure 86 - RP: Maintenance Register (RPMR)

Figure 87 - RP: Drive Type Register (RPDT)

Figure 88 - RP: Serial Number Register (RPSN)

Figure 89 - RP: Offset Register (RPOF)

Figure 90 - RP: Desired Cylinder Register (RPDC)

Figure 91 - RP: Current Cylinder Register (RPCC)

Figure 92 - RP: Error Status #2 (RPER2)

Figure 93 - RP: Error Status #3 (RPER3)

Figure 94 - RP: Error Position Register (RPEC1)

Figure 95 - RP: Error Pattern Register (RPEC2)

Figure 96 - MT: Control and Status Register #1 (MTCS1)

Figure 97 - MT: Frame Register (MTFC)

Figure 98 - MT: Drive Status Register (MTDS)

Figure 99 - MT: Error Register (MTER)

Figure 100 - MT: Attention Summary Register (MTAS)

Figure 101 - MT: Character Check (MTCC)

Figure 102 - MT: Maintenance Register (MTMR)

Figure 103 - MT: Drive Type Register (MTDT)

Figure 104 - MT: Serial Number Register (MTSN)

Figure 105 - MT: Tape Control Register (MTTC)

Figure 106 - MT: Tape Format: PDP-10 Core Dump Format

Figure 107 - MT: Tape Format: PDP-10 Seven Track Format

Figure 108 - MT: Tape Format: PDP-10 ASCII Format

Figure 109 - MT: Tape Format: PDP-10 Compatible Format

Figure 110 - DZ: DZ11 Block Diagram

Figure 111 - DZ: Control and Status Register (DZCSR)

Figure 112 - DZ: Receiver Buffer Register (DZRBUF)

Figure 113 - DZ: Line Parameter Register (DZLPR)

Figure 114 - DZ: Transmit Control Register (DZTCR)

Figure 115 - DZ: Modem Status Register (DZMSR)

Figure 116 - DZ: Transmit Data Register (DZTDR)

Figure 117 - LP: Control/Status Register A (LPCSRA)

Figure 118 - LP: Control/Status Register B (LPCSRB)

Figure 119 - LP: Bus Address Register (LPBAR)

Figure 120 - LP: Byte Count Register (LPBCTR)

Figure 121 - LP: Page Count Register (LPPCTR)

Figure 122 - LP: RAM Data Register (LPRAMD)

Figure 123 - LP: Column Counter Register (LPCCTR) / Character Buffer Register (LPCBUF)

Figure 124 - LP: Printer Data Register (LPPDAT) / Checksum Register (LPCKSM)

Figure 125 - LP: LP26 Printer Photo

Figure 126 - LP: LP26 Printer Data Munging

Figure 127 - DUP: SDLC/ADCCP Protocol

Figure 128 - DUP: DDCMP/BISYNC Protocol

Figure 129 - DUP: Receiver Control/Status Register (RXCSR)

Figure 130 - DUP: Received Data Buffer (RXDBUF)

Figure 131 - DUP: Parameter Control/Status Register (PARCSR)

Figure 132 - DUP: Transmitter Control/Status Register (TXCSR)

Figure 133 - DUP: Transmitter Data Buffer (TXDBUF)

Figure 134 - KMC: Register Set

Figure 135 - KMC: NPR Control Register (KMCNPRC)

Figure 136 - KMC: MISC Register (KMCMISC)

Figure 137 - UBE: Data Buffer Register (UBEDB)

Figure 138 - UBE: Cycle Count Register (UBECC)

Figure 139 - UBE: Buffer Address Register (UBEBA

Figure 140 - UBE: Control/Status Register #1 (UBECSR1)

Figure 141 - UBE: Clear Error Register (UBECLR)

Figure 142 - UBE: Control/Status Register #2 (UBECSR2)

Figure 143 - UBE: Simultaneous GO Register (SIMGO)

Table 1 - BUS: KS10 Bus Arbiter Operations

Table 2 - BUS: KS10 Address Flag Definitions

Table 3 - CON: KS10 Interface Register Inventory

Table 4 - CON: KS10 Console Control/Status Register Definitions

Table 5 - CON: DZ11 Console Control Register (DZCCR) Definition

Table 6 - CON: LP20 Console Control Register (LPCCR) Definitions

Table 7 - CON: MT Console Control Register (MTCCR)

Table 8 - CON: RP Console Control Register (RPCCR)

Table 9 - CON: DUP11 Console Control Register (DUPCCR) Definition

Table 10 - CON: KS10 Breakpoint Address Register (BRAR[0:3]) Definitions

Table 11 - CON: KS10 Breakpoint Mask Register (BRMR[0:3]) Definitions

Table 12 - CON: KS10 Instruction Trace Register (ITR) Definitions

Table 13 - CON: KS10 Program Counter and Instruction Register (PCIR) Definitions

Table 14 - CON: MT Data Interface Register (MTDIR)

Table 15 - CON: MT Debug Register (MTDEBUG) Definitions

Table 16 - CON: RP Debug Register (RPDEBUG) Definitions

Table 17 - CON: KS10 Firmware Version Register (FVR) Definitions

Table 18 - CON: KS10 Control Interface

Table 19 - CON: KS10 Console Communications Area

Table 20 - CON: KS10 Halt Switch (KS10 Memory Address 000030)

Table 21 - CON: KS10 Keep Alive Word (KS10 Memory Address 000031)

Table 22 - CON: KS10 CTY Output Word (KS10 Memory Address 000032)

Table 23 - CON: KS10 CTY Output Word (KS10 Memory Address 000032)

Table 24 - CON: KS10 KLINIK Input Word (KS10 Memory Address 000034)

Table 25 - CON: KS10 KLINIK Output Word (KS10 Memory Address 000035)

Table 26 - CON: KS10 Boot RH11 Address Word (KS10 Memory Address 000036)

Table 27 - CON: KS10 Boot Unit Number (KS10 Memory Address 000037)

Table 28 - CON: KS10 Boot Magtape Parameter Word (KS10 Memory Address 000040)

Table 29 - CPU: KS10 Microcode Variations

Table 30 - CPU: KS10 RAMFILE Addressing

Table 31 - MEM: Memory Controller Register Summary

Table 32 - MEM: Memory Status Register (MSR) Definitions

Table 33 - UBA: Register Summary

Table 34 - UBA: Status Register (UBASR) Definitions - IO Address 763100

Table 35 - UBA: Maintenance Register (UBAMR) Definitions - IO Address 763101

Table 36 - UBA: Paging RAM Definitions - IO Addresses 763000-763077

Table 37 - UBA: Byte and Word Address Translation

Table 38 - UBA: Supported Device NPR Operations

Table 39 - RH: Configuration

Table 40 - RH: Device Registers

Table 41 - RH: Massbus Register Address Cross Reference

Table 42 - RH: Control and Status Register #1 (RHCS1) – IO Address 776700

Table 43 - RH: Word Count Register (RHWC) – IO Address 776702

Table 44 - RH: Bus Address Register (RHBA) – IO Address 776704

Table 45 - RH: Control and Status Register #2 (RHCS2) – IO Address 776710

Table 46 - RH: Data Buffer Register (RHDB) – IO Address 776722

Table 47 - RP: Common PDP-10 Disk Parameters

Table 48 - RP: Device Registers

Table 49 - RP: Control and Status Register #1 (RPCS1) – IO Address 776700

Table 50 - RP: Disk Address Register (RPDA) – IO Address 776706

Table 51 - RP: Drive Status Register (RPDS) – IO Address 776712

Table 52 - RP: Error Register #1 (RPER1) – IO Address 776714

Table 53 - RP: Attention Summary (RPAS) – IO Address 776716

Table 54 - RP: Look Ahead (RPLA) – IO Address 776720

Table 55 - RP: Maintenance Register (RPMR) – IO Address 776724

Table 56 - RP: Drive Type Register (RPDT) – IO Address 776726

Table 57 - RP: Serial Number Register (RPSN) – IO Address 776730

Table 58 - RP: Offset Register (RPOF) – IO Address 776732

Table 59 - RP: Desired Cylinder (RPDC) – IO Address 776734

Table 60 - RP: Current Cylinder (RPCC) – IO Address 776736

Table 61 - RP: Error Status Register #2 (RPER2) – IO Address 776740

Table 62 - RP: Error Status Register #3 (RPER3) – IO Address 776742

Table 63 - RP: Error Position Register (RPEC1) – IO Address 776744

Table 64 - RP: Error Pattern Register (RPEC2) – IO Address 776746

Table 65 - RP: Command Function Codes

Table 66 - MT: Device Registers

Table 67 - MT: Control and Status Register #1 (MTCS1) – IO Address 772440

Table 68 - MT: Frame Count Register (MTFC) – IO Address 772446

Table 69 - MT: Drive Status Register (MTDS) – IO Address 772452

Table 70 - MT: Error Register (MTER) – IO Address 772454

Table 71 - MT: Attention Summary (MTAS) – IO Address 772456

Table 72 - MT: Character Check (MTCC) – IO Address 772460

Table 73 - MT: Maintenance Register (MTMR) – IO Address 772464

Table 74 - MT: Drive Type Register (MTDT) – IO Address 776726

Table 75 - MT: Serial Number Register (MTSN) – IO Address 772470

Table 76 - MT: Tape Control Register (MTTC) – IO Address 772472

Table 77 - MT: Command Function Codes

Table 78 - MT: Data Interface Register (MTDIR)

Table 79 - MT: Timing Parameters

Table 80 - DZ: DZ11 Configuration

Table 81 - DZ: DZ11 Register Summary

Table 82 - DZ: Control/Status Register (DZCSR) - IO Address 760010

Table 83 - DZ: Receiver Buffer Register (DZRBUF) - IO Address 760012

Table 84 - DZ: Line Parameter Register (DZLPR) - IO Address 760012

Table 85 - DZ: Transmit Control Register (DZTCR) - IO Address 760014

Table 86 - DZ: Modem Status Register (DZMSR) - IO Address 760016

Table 87 - DZ: Transmitter Data Register (DZTDR) - IO Address 760016

Table 88 - LP: LP20 Register Summary

Table 89 - LP: Control/Status A Register (LPCSRA) - IO Address 775400

Table 90 - LP: Control/Status B Register (LPCSRB) - IO Address 775402

Table 91 - LP: Bus Address Register (LPBAR) - IO Address 775404

Table 92 - LP: Byte Count Register (LPBCTR) - IO Address 775406

Table 93 - LP: Page Count Register (LPPCTR) - IO Address 775410

Table 94 - LP: RAM Data Register (LPRAMD) - IO Address 775412

Table 95 - LP: LP26 Characteristics

Table 96 - LP: LP26 Absolute Motion Commands

Table 97 - LP: LP26 Slew Commands

Table 98 - DUP: DUP11 Configuration

Table 99 - DUP: DUP11 Register Summary

Table 100 - DUP: RX Control/Status Register (RXCSR) – IO Address 760300

Table 101 - DUP: RX Data Buffer Register (RXDBUF) – IO Address 760302

Table 102 - DUP: Param Control/Status Register (PARCSR) - IO Address 760302

Table 103 - DUP: TX Control/Status Register (TXCSR) - IO Address 760304

Table 104 - DUP: TX Data Buffer (TXDBUF) - IO Address 760306

Table 105 - KMC: KMC11 Configuration

Table 106 - KMC: KMC11 Register Summary

Table 107 - KMC: Maintenance Register (KMCMAINT) – IO Address 760541

Table 108 - KMC: Maintenance Address Register (KMCMAR) – IO Address 760544

Table 109 - KMC: Maintenance Instruction Register (KMCMIR) – IO Address 760546

Table 110 - KMC: NPR Control Register (KMCNPRC)

Table 111 - KMC: MISC Register (KMCMISC)

Table 112 - UBE: Unibus Adapter Exerciser Configuration

Table 113 - UBE: Register Summary

Table 114 - UBE: Data Buffer Register (UBEDB) – IO Offset 0

Table 115 - UBE: Cycle Count Register (UBECC) – IO Offset 2

Table 116 - UBE: Buffer Address Register (UBEBA) – IO Offset 4

Table 117 - UBE: Control/Status Register #1 (UBECSR1) – IO Offset 6

Table 118 - UBE: Clear Error Register (UBECLR) – IO Offset o10

Table 119 - UBE: Control/Status Register #2 (UBECSR2) – IO Offset o16

Table 120 - UBE: Simultaneous GO Register (SIMGO) – IO Address 770014

Table 121 - DSKFAA0 Benchmark Timing

The Digital Equipment Corporation (DEC) KS10 was a low cost implementation of the popular PDP-10 mainframe computer. I learned to how to program computers while typing on a VT52 on the Penn State KA10 - and I’ve always wanted to own a PDP-10. That'll never happen, but maybe I can build my own...

Some photos of a KS10 are illustrated below:

|

Figure 1 - The DEC KS10 (Photo from LCM) |

Figure 2 - The DEC KS10 with Covers Removed (Photo from RICM) |

Figure 3 - KS10 FPGA in Mini-ITX chassis

The goal of this project is to re-implement the DEC KS10 using modern components and technology. It is intended that this will closely, but not exactly, replicate the KS10 design in FPGA hardware. I have no desire to exactly replicate the KS10 timing: there are too many places where the logic is difficult to replicate. The DEC KS10 used a lot of asynchronous parts (asynchronous memory, asynchronous logic, FIFOs/SILOs, one-shots, delay lines, RC delays, etc) that don't map very well to modern components - especially FPGAs. I've elected to redesign circuitry as necessary to use the FPGA resources. This project will retain microcode compatibility with the DEC KS10.

The DEC KS10 was implemented in 1978 using AMD am29xx TTL bit-slice device and 74LSxx SSI and MSI devices. The DEC KS10 had a 6.66 MHz clock cycle.

The DEC KS10 consisted of the following circuit boards:

- 4 board CPU set

- Console based on Intel 8080 microprocessor

- Memory Controller

- 8 Memory boards (64K x 36 with ECC)

- 2 (or more) Unibus Adapters

- Disk IO (RH11/RP)

- TTY IO (DZ11)

- Tape Unit (RH11/TM03/TU)

- Power Supply

In addition to implementing these basic functions, the KS10 FPGA implements:

- Synchronous COM Unit (DUP11)

- General Purpose Processor (KMC11)

- Printer controller and printer (LP20/LP26)

- 3rd Unibus Adapter (UBA4)

- Unibus Exercisers

The CPU, Console, Memory Controller, and Unibus Adapters boards are all interconnected by the KS10 backplane bus.

The Console Processor and the entire KS10 Central Processing Unit (CPU) is implemented in a single Intel Cyclone 5 System on a Chip (SoC) Field Programmable Gate Array (FPGA). In addition to the FPGA, this SoC includes a dual core ARM processor which provides the platform for the Console Processor and provides capabilities for modern networking. The FPGA is firmware is written in Verilog and currently consists of about 33,000 lines of code plus comments. The Console Software is multi-threaded Linux application that is written in C++.

The KS10 FPGA peripherals are significantly different than the legacy DEC KS10 peripherals. Modern peripherals like Secure Digital High-Capacity (SDHC) solid-state disk drives replace the Moving Head RP06 disk drives and TU77 9-track magtape drives. Even though the physical devices are different, the original hardware interfaces have been retained. The disk drives use the same bits-on-disk formatting as the SIMH simulator so that files and disk images may be moved between SIMH and the target hardware without modification. Universal Serial Bus (USB) and Ethernet devices are provided in addition to standard legacy RS-232 devices.

A block diagram of the KS10 FPGA is presented below:

Figure 4 - KS10 FPGA Block Diagram

The latest revision of the KS10 FPGA Processor Manual is available from: KS10 FPGA Processor Manual (Rev 47)] Please note that the Processor Manual is not actively maintained as most of the documentation has been shifted to this WIKI.

DSKAAA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 1) . . . . . . . . . . . . Pass DSKABA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 2) . . . . . . . . . . . . Pass DSKACA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 3) . . . . . . . . . . . . Pass DSKADA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 4) . . . . . . . . . . . . Pass DSKAEA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 5) . . . . . . . . . . . . Pass DSKAFA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 6) . . . . . . . . . . . . Pass DSKAGA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 7) . . . . . . . . . . . . Pass DSKAHA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 8) . . . . . . . . . . . . Pass DSKAIA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC ( 9) . . . . . . . . . . . . Pass DSKAJA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC (10) . . . . . . . . . . . . Pass DSKAKA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC (11) . . . . . . . . . . . . Pass DSKALA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC (12) . . . . . . . . . . . . Pass DSKAMA0 DECSYSTEM 2020 BASIC INSTRUCTION DIAGNOSTIC (13) . . . . . . . . . . . . Pass DSKBAA0 DECSYSTEM 2020 BASIC INSTRUCTION RELIABILITY DIAGNOSTIC . . . . . . . . Pass DSKCAA0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (1) . . . . . . . . . . . Pass DSKCBA0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (2) . . . . . . . . . . . Pass DSKCCA0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (3) . . . . . . . . . . . Pass DSKCDA0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (4) . . . . . . . . . . . Pass DSKCEA0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (5) . . . . . . . . . . . Pass DSKCFC0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (6) . . . . . . . . . . . Pass DSKCGB0 DECSYSTEM 2020 ADVANCED INSTRUCTION DIAGNOSTIC (7) . . . . . . . . . . . . . Fail DSKDAB0 DECSYSTEM 2020 CPU AND MEMORY RELIABILITY DIAGNOSTIC . . . . . . . . . . . . Fail DSKEAA0 DECSYSTEM 2020 PAGING HARDWARE DIAGNOSTIC . . . . . . . . . . . . . . . . . Fail DSKEBA0 KS10 - CACHE DIAGNOSTIC . . . . . . . . . . . . . . . . . . . . . . . . Pass* DSKECB0 KS10 - KL-PAGING DIAGNOSTIC . . . . . . . . . . . . . . . . . . . . . . . . Fail DSKFAA0 DECSYSTEM 2020 INSTRUCTION TIMING DIAGNOSTIC . . . . . . . . . . . . . . Pass DSDUAB0 DSDUA DECSYSTEM 2020 DUP-11 DIAGNOSTICS . . . . . . . . . . . . . . . . Pass DSDZAB0 DECSYSTEM 2020 DZ11 ASYNC. LINE MUX DIAGNOSTICS (DSDZA). . . . . . . . . Pass DSKMAA0 DECSYSTEM 2020 KMC11 DIAGNOSTICS . . . . . . . . . . . . . . . . . . . . Pass DSLPA DECSYSTEM 2020 LINE PRINTER DIAGNOSTIC [DSLPA] . . . . . . . . . . . . . Pass DSLTA DECSYSTEM 2020 TELETYPE TEST . . . . . . . . . . . . . . . . . . . . . . Pass DSMMAB0 DECSYSTEM 2020 KS10 1024K MEMORY DIAGNOSTIC (DSMMA) . . . . . . . . . . Pass DSMMBA0 DECSYSTEM 2020 BLT/FLOATING 1-0 MEMORY EXERCISER TEST (DSMMB) . . . . . Pass DSMMCB0 DECSYSTEM 2020 FAST AC DIAGNOSTIC (DSMMC) . . . . . . . . . . . . . . . Pass DSMMDC0 DECSYSTEM 2020 MEMORY DIAGNOSTIC (DSMMD) . . . . . . . . . . . . . . . . Pass DSRMAB0 DECSYSTEM 2020 RM03-RH11 BASIC DRIVE DIAGNOSTIC . . . . . . . . . . . . . . Fail DSRMB DECSYSTEM 2020 RH11 - RM03/RP06 - RELIABILITY DIAGNOSTIC . . . . . . . . . . Fail DSRPAC0 DECSYSTEM 2020 RP06-RH11 BASIC DRIVE DIAGNOSTIC [DSRPA] . . . . . . . . Pass** DSTUA DECSYSTEM 2020 RH11-TM02/03-TU45/TU77 BASIC DEVICE DIAGNOSTIC (DSTUA) . . . Fail DSTUB DECSYSTEM 2020 RH11-TM02/03-TU16/TU45/TU77 RELIABILITY DIAGNOSTIC(DSTUB) Pass DSUBAC0 DECSYSTEM 2020 UNIBUS ADAPTER EXERCISER [ DSUBA ] . . . . . . . . . . . Pass

* This includes expected failures because the cache is not implemented. The FPGA main memory uses very fast Synchronous SRAM that can perform reads and writes in a single CPU clock cycle - just like a cache.

** This includes expected failures because parts of the RP06 Diagnostic Mode is not implemented. The RP06 Diagnostic Mode is only used by the diagnostic program and is not required for any of the Monitor programs.

The KS10 Hardware Documents (schematics) are available from: http://www.bitsavers.org/pdf/dec/pdp10/KS10/

KS10 Software is available from: http://pdp-10.trailing-edge.com/

All software development and FPGA firmware development is performed on a host computer that is attached to the KS10 FPGA target device.

Currently most of the development is performed on a Cygwin (Windows) system, for now. Gradually, the build system is being expanded to build the KS10 project using Linux tools and/or using the Windows System for Linux (WSL) tools. This tool expansion is on-going.

Numerous unix utilities are employed to automate the build processes. Performing these tasks manually would be onerous and prone to mistakes. There are no plan to expand the development tooling to use non-unix -like tools.

The Host Computer system is used to build the software, to build the FPGA firmware, and to build and run the simulation tooling.

The KS10 FPGA software uses some submodules that are maintained outside of the KS10 FPGA repository. You must clone the repository as follows:

$ cd <install_directory> $ git clone --recurse-submodules https://github.com/KS10FPGA/KS10FPGA

For your reference I've illustrated the directory structure of my build tree below.

Note: Some directories are private (for now) have been not been exported to github.

$ tree -d

.

├── Tape and Disk Images

│ ├── Console SDHC

│ ├── DE10-Nano Image

│ ├── KLAD Sources

│ ├── KS10 Diagnostics

│ ├── KS10 Formatter

│ ├── KS10 Microcode

│ ├── RED PACK 405A2

│ ├── TOPS10

│ └── TOPS20

├── code

│ ├── fpga_loader_prog

│ └── gpio

├── fpga

│ ├── de10_top

│ │ ├── ise

│ │ ├── iverilog

│ │ ├── quartus

│ │ └── questa

│ ├── ks10

│ │ ├── arb

│ │ ├── breakpoint

│ │ ├── cpu

│ │ │ └── useq

│ │ ├── csl

│ │ ├── debug

│ │ ├── dup11

│ │ ├── dz11

│ │ ├── kmc11

│ │ ├── lp20

│ │ ├── lp26

│ │ ├── mem

│ │ ├── mt

│ │ ├── rh11

│ │ ├── rpxx

│ │ │ └── sd

│ │ ├── trace

│ │ ├── uba

│ │ ├── ube

│ │ └── utils

│ │ ├── uart

│ │ └── usrt

│ └── testbench

├── maindec

├── microcode

│ ├── ITS

│ ├── V130

│ └── V130R1

├── tools

│ ├── asm10

│ ├── mtdump

│ ├── seqparse

│ └── tapeutils

└── wiki

└── images

├── cpu

├── csl

├── dup11

├── dz11

├── hw

├── kmc11

├── lp20

├── lp26

├── mem

├── mt

├── rh11

├── rpxx

└── uba

The KS10 Console Processor application is a multi-threaded Linux application that controls and interacts with the the KS10 processor.

The console software can be built four different ways:

- cross-compiled on a Cygwin host, or

- cross-compiled on a Linux host, or

- cross-compiled on a Windows Subsystem for Linux (WSL) host, or

- compiled natively on the target.

Of all the options, cross-compiling the software is definitely the fastest.

These build processes are illustrated below.

Yes I know that I run the DE10-Nano target as root. Yes I'm aware that there are good reasons not to do that.

The Cygwin build uses an ARM cross-compiler to buld the target software and then transfers the binary executable to the DE10-Nano target using Secure Copy (scp).

The installation procedure for the ARM cross-compiler is detailed in the Host Software section of this wiki.

Note: The executable is statically linked so that the libraries on the DE10-Nano don't have to match the libraries on the host system.

The software is built in the code directory as follows:

$ cd code $ make arm-none-linux-gnueabihf-g++ -static -Os -W -Wall -pthread -pipe -Wformat=0 commands.cpp config.cpp cursor.cpp dasm.cpp dz11.cpp dup11.cpp hist.cpp cmdline.cpp ks10.cpp lp20.cpp mt.cpp rp.cpp rh11.cpp tape.cpp main.cpp -o console make xfer make[1]: Entering directory '/cygdrive/f/pdpx/pdp10/ks10/code' scp -B console root@ks10:/home/root/ console 100% 4134KB 2.3MB/s 00:01 make[1]: Leaving directory '/cygdrive/f/pdpx/pdp10/ks10/code'

The WSL build uses an ARM cross-compiler to buld the target software and then transfers the binary executable to the DE10-Nano target using Secure Copy (scp).

The installation procedure for the ARM cross-compiler is detailed in the Host Software section of this wiki.

Note: The executable is statically linked so that the libraries on the DE10-Nano don't have to match the libraries on the host system.

The software is built in the code directory as follows:

$ cd code $ make arm-linux-gnueabihf-g++ -static -Os -W -Wall -pthread -pipe -Wformat=0 commands.cpp config.cpp cursor.cpp dasm.cpp dz11.cpp dup11.cpp hist.cpp cmdline.cpp ks10.cpp lp20.cpp mt.cpp rp.cpp rh11.cpp tape.cpp main.cpp -o console make xfer make[1]: Entering directory '/mnt/f/pdpx/pdp10/ks10/code' scp -B console root@ks10:/home/root/ console 100% 1102KB 5.0MB/s 00:00 make[1]: Leaving directory '/mnt/f/pdpx/pdp10/ks10/code'

The source files may be copied to the DE10-Nano target and compiled natively as follows:

$ make g++ -O2 -W -Wall -pthread -pipe -Wformat=0 commands.cpp config.cpp cursor.cpp dasm.cpp dz11.cpp dup11.cpp hist.cpp cmdline.cpp ks10.cpp lp20.cpp mt.cpp rp.cpp rh11.cpp tape.cpp main.cpp -o console make xfer make[1]: Entering directory '/home/root' make[1]: Nothing to be done for 'xfer'. make[1]: Leaving directory '/home/root'

For now, the FPGA build process requires the Cygwin environment using Quartus 18.1.

As stated above, the FPGA build process requires the Cygwin environment using Quartus 18.1.

I have Quartus 21.1 for Windows installed but the

qsys-generate build fails using my scripts as

well as when using the Quartus IDE.

Apparently it is a known issue and the workaround is to use Linux.

I tried the workaround described at:

https://forum.rocketboards.org/t/de10-nano-manual-instructions-fail-to-compile-ghrd-on-ubuntu-solved/1282

and didn't have any success - but I haven't spent much time debugging this.

All of the other Quartus 21.1 executables work properly.

I also have Quartus 21.1 for Linux using WSL installed. The qsys-generate

build also fails using my script as well as when using the Quartus IDE. It

fails differently -- it hangs forever with no progress after a certain point.

Both Quartus 21.1 for Windows and Quartus 21.1 for Linux both build the

the rest of the FPGA firmware which is everything but the SOC. It is only

qsys-generate that is broken.

I was also unable to make the Quartus Linux tool recognize the USB

Programmer. It fails with a

Error (213013): Programming hardware cable not detected

message.

I tried all the fixes at: https://www.jackenhack.com/quartus-prime-fpga-usb-blaster-problems-ubuntu-18-04/. Nothing affected this issue. I think the issue is related to WSL not forwarding the USB device into the virtual machine and is not related to Linux. See below:

$ lsusb Bus 002 Device 001: ID 1d6b:0003 Linux Foundation 3.0 root hub Bus 001 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

The FPGA Firmware build process is rather elaborate and roughly proceeds as follows:

- Extract the microcode from the DEC microcode listing files. The KS10 FPGA contains two microcode ROMS: the Dispatch ROM and the Control ROM which are both part of the microsequencer. A pair of awk scripts (crom.awk and drom.awk) extract the microcode from the DEC microcode listing file and generate files that are used to initialize the two ROMS. Lastly, the KS10 CPU Serial Number is built into the microcode. The "crom.awk" microcode extraction tool also edits the microcode to store a non-default KS10 CPU Serial Number in the microcode.

- Quartus "qsys-generate" (aka Plaform Designer) takes the system-on-a-chip (SOC) description files and generates the top level SOC verilog files which can built with the KS10 RTL files. The SOC description files include things like the interface beteen the FPGA fabric and the Intel Hard Processing System (HPS) This interface includes memory interfaces, peripheral interfaces, the AXI4-lite slave interface which is the primary interface between the KS10 and the ARM processors, interrupts, GPIO, etc.

- "quartus-map" analyzes and synthesizes the design.

- "quartus-fit" place-and-routes the design.

- "quartus-asm" assembles the design and creates and SRAM Object File (".sof").

- "quartus-sta" peforms a static timing analysis.

- Optionally "quartus-pgm" programs the FPGA (not the flash) via the JTAG interface.

The fpga/makefile has several targets that are useful when

building the FPGA firmware.

The default target simply builds the FPGA firmware and creates the "de10_ks10.sof" SRAM Object File. The "de10_ks10.sof" file is used later to program the FPGA. This is illustrated below:

$ make

The "pgm1" target will load whatever firmware is already built into the FPGA via the JTAG interface.

$ make pgm1

The "pgm" target builds the FPGA firmware, creates the "de10_ks10.sof" file, and loads the firmware into the FPGA via the JTAG interface as follows:

$ make pgm

A transcript of today's build of the FPGA is shown below. Obviously this just a 'snapshot' of the state of the design and will change as the design evolves.

Quartus is notorious for emitting a ton of "less than useful" (annoying) warnings and information messages during the build process. In general there is so junk in the output that it is difficult to find important messages that should not be ignored. I've done my best to filter out the noise and leave the genuinely interesting messages in the output transcript.

$ make pgm

Creating de10_top/quartus/de10_ks10.qsf

Creating de10_top/quartus/files.qsf

awk -v SERIALNUM=4097 -f ks10/cpu/useq/crom.awk < ks10/cpu/useq/ks10.mcr > ks10/cpu/useq/crom.dat

/cygdrive/c/intelFPGA_lite/18.1/quartus/bin64/quartus_map --read_settings_files=on --write_settings_files=off --rev=de10_ks10 --verilog_macro=QUARTUS \

--verilog_macro=SYNTHESIS --verilog_macro=SERIALNUM=4097 --verilog_macro=MAJOR_VER=\"00\" --verilog_macro=MINOR_VER=\"37\" --verilog_macro=CLKFRQ=12500000 \

--verilog_macro=SSRAMx18 --verilog_macro=RPXX_SIMSEEK --verilog_macro=RPXX_SIMDMD --verilog_macro=UBA1 --verilog_macro=RH11A --verilog_macro=UBA3 \

--verilog_macro=RH11B --verilog_macro=LP20 --verilog_macro=DZ11 --verilog_macro=DUP11 --verilog_macro=KMC11 --verilog_macro=UBA4 --verilog_macro=UBE1 \

--verilog_macro=UBE2 --verilog_macro=UBE3 --verilog_macro=UBE4 de10_top/quartus/de10_ks10

Info: *******************************************************************

Info: Running Quartus Prime Analysis & Synthesis

Info: Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Info: Copyright (C) 2018 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the applicable agreement for further details.

Info: Processing started: Sat Mar 05 04:14:13 2022

Info: Command: quartus_map --read_settings_files=on --write_settings_files=off --rev=de10_ks10 --verilog_macro=QUARTUS --verilog_macro=SYNTHESIS \

--verilog_macro=SERIALNUM=4097 --verilog_macro=MAJOR_VER="00" --verilog_macro=MINOR_VER="37" --verilog_macro=CLKFRQ=12500000 --verilog_macro=SSRAMx18 \

--verilog_macro=RPXX_SIMSEEK --verilog_macro=RPXX_SIMDMD --verilog_macro=UBA1 --verilog_macro=RH11A --verilog_macro=UBA3 --verilog_macro=RH11B \

--verilog_macro=LP20 --verilog_macro=DZ11 --verilog_macro=DUP11 --verilog_macro=KMC11 --verilog_macro=UBA4 --verilog_macro=UBE1 --verilog_macro=UBE2 \

--verilog_macro=UBE3 --verilog_macro=UBE4 de10_top/quartus/de10_ks10

Info (20032): Parallel compilation is enabled and will use up to 16 processors

Info (12127): Elaborating entity "de10_ks10" for the top level hierarchy

Warning (10034): Output port "ESD_ADDR" at de10_ks10.v(160) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 160

Warning (10034): Output port "ESD_SCLK" at de10_ks10.v(153) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 153

Warning (10034): Output port "ESD_DO" at de10_ks10.v(155) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 155

Warning (10034): Output port "ESD_CS_N" at de10_ks10.v(156) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 156

Warning (10034): Output port "ESD_RST_N" at de10_ks10.v(157) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 157

Warning (10034): Output port "ESD_RD_N" at de10_ks10.v(158) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 158

Warning (10034): Output port "ESD_WR_N" at de10_ks10.v(159) has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 159

Warning (10030): Net "dupTXFIFO" at ks10.sv(347) has no driver or initial value, using a default initial value '0' File: F:/pdpx/pdp10/ks10/fpga/ks10/ks10.sv Line: 347

Warning (10030): Net "dupTXE" at ks10.sv(338) has no driver or initial value, using a default initial value '0' File: F:/pdpx/pdp10/ks10/fpga/ks10/ks10.sv Line: 338

Warning (10030): Net "dupRXF" at ks10.sv(348) has no driver or initial value, using a default initial value '0' File: F:/pdpx/pdp10/ks10/fpga/ks10/ks10.sv Line: 348

Info (10008): Verilog HDL or VHDL information: EDA Netlist Writer cannot regroup multidimensional array "wire_to_nowhere_64" into its bus

Info (10041): Inferred latch for "dpreg[35]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[34]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[33]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[32]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[31]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[30]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[29]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[28]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[27]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[26]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[25]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[24]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[23]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[22]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[21]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[20]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[19]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[18]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[17]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[16]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[15]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[14]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[13]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[12]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[11]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[10]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[9]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[8]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[7]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[6]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[5]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[4]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[3]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[2]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[1]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10041): Inferred latch for "dpreg[0]" at cpu.sv(202) File: F:/pdpx/pdp10/ks10/fpga/ks10/cpu/cpu.sv Line: 202

Info (10264): Verilog HDL Case Statement information at debug.v(102): all case item expressions in this case statement are onehot File: F:/pdpx/pdp10/ks10/fpga/ks10/debug/debug.v Line: 102

Info (10264): Verilog HDL Case Statement information at uart_tx.v(392): all case item expressions in this case statement are onehot File: F:/pdpx/pdp10/ks10/fpga/ks10/utils/uart/uart_tx.v Line: 392

Info (19000): Inferred 15 megafunctions from design logic

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|RH11:uRH11B|RHDB:DB|mem_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|KMC11:uKMC11|KMCMEM:uMEM|ram_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|KMC11:uKMC11|KMCSEQ:uSEQ|kmcCRAM_MEM_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|LP26:uLP26|lpDVFUDAT_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|LP26:uLP26|lpLINBUF_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|LP20:uLP20|LPRAMD:RAMD|ramDATA_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|LP20:uLP20|LPRAMD:RAMD|ramCTRL_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|DZ11:uDZ11|DZRBUF:RBUF|FIFO:RBUF|mem_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|RH11:uRH11A|RHDB:DB|mem_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|DEBUG:uDEBUG|FIFO:TRACE_BUFFER|mem_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|CPU:uCPU|RAMFILE:uRAMFILE|ram_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|CPU:uCPU|PAGER:uPAGER|pageTABLE_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|CPU:uCPU|USEQ:uUSEQ|STACK:uSTACK|stack_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|CPU:uCPU|USEQ:uUSEQ|CROM:uCROM|CROM_rtl_0"

Info (276029): Inferred altsyncram megafunction from the following design logic: "soc_system:u0|KS10:ks10|CPU:uCPU|DROM:uDROM|DROM_rtl_0"

Warning (14284): Synthesized away the following node(s):

Warning (14285): Synthesized away the following RAM node(s):

Warning (13039): The following bidirectional pins have no drivers

Warning (13040): bidirectional pin "ESD_DIO" has no driver File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 161

Warning (13009): TRI or OPNDRN buffers permanently enabled

Warning (13024): Output pins are stuck at VCC or GND

Warning (13410): Pin "LED_PWR_N" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 148

Warning (13410): Pin "LED_BOOT_N" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 150

Warning (13410): Pin "ESD_SCLK" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 153

Warning (13410): Pin "ESD_DO" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 155

Warning (13410): Pin "ESD_CS_N" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 156

Warning (13410): Pin "ESD_RST_N" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 157

Warning (13410): Pin "ESD_RD_N" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 158

Warning (13410): Pin "ESD_WR_N" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 159

Warning (13410): Pin "ESD_ADDR[0]" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 160

Warning (13410): Pin "ESD_ADDR[1]" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 160

Warning (13410): Pin "ESD_ADDR[2]" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 160

Warning (13410): Pin "ESD_ADDR[3]" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 160

Warning (13410): Pin "ESD_ADDR[4]" is stuck at GND File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 160

Info (286031): Timing-Driven Synthesis is running on partition "Top"

Info (17049): 320 registers lost all their fanouts during netlist optimizations.

Info (286031): Timing-Driven Synthesis is running on partition "soc_system_hps_hps_io_border:border"

Info (144001): Generated suppressed messages file F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/output_files/de10_ks10.map.smsg

Info (16010): Generating hard_block partition "hard_block:auto_generated_inst"

Info (16011): Adding 14 node(s), including 0 DDIO, 4 PLL, 0 transceiver and 0 LCELL

Warning (21074): Design contains 12 input pin(s) that do not drive logic

Warning (15610): No output dependent on input pin "SW_BOOT_N" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 146

Warning (15610): No output dependent on input pin "SW_HALT_N" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 147

Warning (15610): No output dependent on input pin "ESD_DI" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 154

Warning (15610): No output dependent on input pin "KEY[0]" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 163

Warning (15610): No output dependent on input pin "KEY[1]" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 163

Warning (15610): No output dependent on input pin "SW[0]" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 164

Warning (15610): No output dependent on input pin "SW[1]" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 164

Warning (15610): No output dependent on input pin "SW[2]" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 164

Warning (15610): No output dependent on input pin "SW[3]" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 164

Warning (15610): No output dependent on input pin "SPARE0" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 165

Warning (15610): No output dependent on input pin "SPARE1" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 166

Warning (15610): No output dependent on input pin "SPARE2" File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 168

Info (21057): Implemented 27513 device resources after synthesis - the final resource count might be different

Info (21058): Implemented 37 input pins

Info (21059): Implemented 102 output pins

Info (21060): Implemented 84 bidirectional pins

Info (21061): Implemented 26305 logic cells

Info (21064): Implemented 332 RAM segments

Info (21065): Implemented 4 PLLs

Info (21066): Implemented 1 delay-locked loops

Info: Quartus Prime Analysis & Synthesis was successful. 0 errors, 42 warnings

Info: Peak virtual memory: 5457 megabytes

Info: Processing ended: Sat Mar 05 04:18:39 2022

Info: Elapsed time: 00:04:26

Info: Total CPU time (on all processors): 00:03:42

/cygdrive/c/intelFPGA_lite/18.1/quartus/bin64/quartus_fit --read_settings_files=off --write_settings_files=off --rev=de10_ks10 de10_top/quartus/de10_ks10

Info: *******************************************************************

Info: Running Quartus Prime Fitter

Info: Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Info: Copyright (C) 2018 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the applicable agreement for further details.

Info: Processing started: Sat Mar 05 04:18:40 2022

Info: Command: quartus_fit --read_settings_files=off --write_settings_files=off --rev=de10_ks10 de10_top/quartus/de10_ks10

Info: qfit2_default_script.tcl version: #1

Info: Project = de10_ks10

Info: Revision = de10_ks10

Info (20032): Parallel compilation is enabled and will use up to 16 processors

Info (119006): Selected device 5CSEBA6U23I7 for design "de10_ks10"

Info (21077): Low junction temperature is -40 degrees C

Info (21077): High junction temperature is 100 degrees C

Info (171003): Fitter is performing an Auto Fit compilation, which may decrease Fitter effort to reduce compilation time

Info (176045): Design uses memory blocks. Violating setup or hold times of memory block address registers for either read or write operations could cause memory contents to be corrupted. Make sure that all memory block address registers meet the setup and hold time requirements.

Critical Warning (169085): No exact pin location assignment(s) for 72 pins of 223 total pins. For the list of pins please refer to the I/O Assignment Warnings table in the fitter report.

Critical Warning (174073): No exact pin location assignment(s) for 1 RUP, RDN, or RZQ pins of 1 total RUP, RDN or RZQ pins

Info (174074): RUP, RDN, or RZQ pin HPS_DDR3_RZQ not assigned to an exact location on the device File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 78

Info (184020): Starting Fitter periphery placement operations

Warning (177007): PLL(s) placed in location FRACTIONALPLL_X0_Y15_N0 do not have a PLL clock to compensate specified - the Fitter will attempt to compensate all PLL clocks

Info (177008): PLL soc_system:u0|KS10:ks10|altera_pll:PLL|general[0].gpll~FRACTIONAL_PLL

Info (11178): Promoted 5 clocks (5 global)

Info (11162): soc_system:u0|soc_system_hps:hps|soc_system_hps_fpga_interfaces:fpga_interfaces|h2f_rst_n[0]~CLKENA0 with 4 fanout uses global clock CLKCTRL_G11

Info (11162): soc_system:u0|KS10:ks10|altera_pll:PLL|outclk_wire[0]~CLKENA0 with 11740 fanout uses global clock CLKCTRL_G7

Info (11162): soc_system:u0|KS10:ks10|altera_pll:PLL|outclk_wire[1]~CLKENA0 with 41 fanout uses global clock CLKCTRL_G5

Info (11162): soc_system:u0|KS10:ks10|altera_pll:PLL|outclk_wire[3]~CLKENA0 with 41 fanout uses global clock CLKCTRL_G2

Info (11162): soc_system:u0|KS10:ks10|altera_pll:PLL|outclk_wire[2]~CLKENA0 with 5 fanout uses global clock CLKCTRL_G6

Info (11191): Automatically promoted 1 clock (1 global)

Info (11162): FPGA_CLK1_50~inputCLKENA0 with 60 fanout uses global clock CLKCTRL_G4

Info (184021): Fitter periphery placement operations ending: elapsed time is 00:00:03

Warning (335093): The Timing Analyzer is analyzing 36 combinational loops as latches. For more details, run the Check Timing command in the Timing Analyzer or view the "User-Specified and Inferred Latches" table in the Analysis & Synthesis report.

Info (332104): Reading SDC File: 'de10_ks10.sdc'

Warning (332174): Ignored filter at de10_ks10.sdc(45): SSRAM_CLK could not be matched with a clock File: F:/PDPx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.sdc Line: 45

Warning (332049): Ignored set_input_delay at de10_ks10.sdc(45): Argument -clock is an empty collection File: F:/PDPx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.sdc Line: 45

Info (332050): set_input_delay -clock [get_clocks SSRAM_CLK] -max 6.5 [get_ports {SSRAM_D*}] File: F:/PDPx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.sdc Line: 45

Info (332110): Deriving PLL clocks

Info (332110): create_generated_clock -source {u0|ks10|PLL|general[0].gpll~FRACTIONAL_PLL|refclkin} -multiply_by 6 -duty_cycle 50.00 -name {u0|ks10|PLL|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} {u0|ks10|PLL|general[0].gpll~FRACTIONAL_PLL|vcoph[0]}

Info (332110): create_generated_clock -source {u0|ks10|PLL|general[0].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 24 -duty_cycle 50.00 -name {u0|ks10|PLL|general[0].gpll~PLL_OUTPUT_COUNTER|divclk} {u0|ks10|PLL|general[0].gpll~PLL_OUTPUT_COUNTER|divclk}

Info (332110): create_generated_clock -source {u0|ks10|PLL|general[1].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 24 -phase 90.00 -duty_cycle 50.00 -name {u0|ks10|PLL|general[1].gpll~PLL_OUTPUT_COUNTER|divclk} {u0|ks10|PLL|general[1].gpll~PLL_OUTPUT_COUNTER|divclk}

Info (332110): create_generated_clock -source {u0|ks10|PLL|general[3].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 24 -phase 270.00 -duty_cycle 50.00 -name {u0|ks10|PLL|general[3].gpll~PLL_OUTPUT_COUNTER|divclk} {u0|ks10|PLL|general[3].gpll~PLL_OUTPUT_COUNTER|divclk}

Info (332110): create_generated_clock -source {u0|ks10|PLL|general[2].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 24 -phase 180.00 -duty_cycle 50.00 -name {u0|ks10|PLL|general[2].gpll~PLL_OUTPUT_COUNTER|divclk} {u0|ks10|PLL|general[2].gpll~PLL_OUTPUT_COUNTER|divclk}

Info (332151): Clock uncertainty is not calculated until you update the timing netlist.

Info (332104): Reading SDC File: 'soc_system/synthesis/submodules/altera_reset_controller.sdc'

Info (332104): Reading SDC File: 'soc_system/synthesis/submodules/altera_avalon_st_handshake_clock_crosser.sdc'

Info (332104): Reading SDC File: 'soc_system/synthesis/submodules/hps_sdram_p0.sdc'

Info (332151): Clock uncertainty is not calculated until you update the timing netlist.

Info (332104): Reading SDC File: 'soc_system/synthesis/submodules/soc_system_hps_hps_io_border.sdc'

Info (332097): The following timing edges are non-unate. The Timing Analyzer will assume pos-unate behavior for these edges in the clock network.

Info (332098): From: u0|hps|fpga_interfaces|hps2fpga_light_weight|clk to: soc_system:u0|soc_system_hps:hps|soc_system_hps_fpga_interfaces:fpga_interfaces|hps2fpga_light_weight~FF_3425

Info (332098): From: u0|hps|hps_io|border|i2c0_inst|i2c_clk to: soc_system:u0|soc_system_hps:hps|soc_system_hps_hps_io:hps_io|soc_system_hps_hps_io_border:border|i2c0_inst~FF_3393

Info (332098): From: u0|hps|hps_io|border|i2c1_inst|i2c_clk to: soc_system:u0|soc_system_hps:hps|soc_system_hps_hps_io:hps_io|soc_system_hps_hps_io_border:border|i2c1_inst~FF_3393

Info (332098): From: u0|hps|hps_io|border|usb1_inst|usb_ulpi_clk to: soc_system:u0|soc_system_hps:hps|soc_system_hps_hps_io:hps_io|soc_system_hps_hps_io_border:border|usb1_inst~FF_3474

Info (332098): Cell: u0|ks10|PLL|general[0].gpll~FRACTIONAL_PLL from: refclkin to: fbclk

Info (332098): Cell: u0|ks10|PLL|general[0].gpll~PLL_OUTPUT_COUNTER from: vco0ph[0] to: divclk

Info (332098): Cell: u0|ks10|PLL|general[0].gpll~PLL_REFCLK_SELECT from: clkin[0] to: clkout

Info (332098): Cell: u0|ks10|PLL|general[1].gpll~PLL_OUTPUT_COUNTER from: vco0ph[0] to: divclk

Info (332098): Cell: u0|ks10|PLL|general[2].gpll~PLL_OUTPUT_COUNTER from: vco0ph[0] to: divclk

Info (332098): Cell: u0|ks10|PLL|general[3].gpll~PLL_OUTPUT_COUNTER from: vco0ph[0] to: divclk

Info (332123): Deriving Clock Uncertainty. Please refer to report_sdc in the Timing Analyzer to see clock uncertainties.

Info (332152): The following assignments are ignored by the derive_clock_uncertainty command

Info (332171): The following clock uncertainty values are less than the recommended values that would be applied by the derive_clock_uncertainty command

Info (332129): Detected timing requirements -- optimizing circuit to achieve only the specified requirements

Info (332111): Found 27 clocks

Info (332111): Period Clock Name

Info (332111): ======== ============

Info (332111): 20.000 FPGA_CLK1_50

Info (332111): 2.500 HPS_DDR3_CK_N

Info (332111): 2.500 HPS_DDR3_CK_P

Info (332111): 2.500 HPS_DDR3_DQS_N[0]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_N[1]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_N[2]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_N[3]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_P[0]_IN

Info (332111): 2.500 HPS_DDR3_DQS_P[0]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_P[1]_IN

Info (332111): 2.500 HPS_DDR3_DQS_P[1]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_P[2]_IN

Info (332111): 2.500 HPS_DDR3_DQS_P[2]_OUT

Info (332111): 2.500 HPS_DDR3_DQS_P[3]_IN

Info (332111): 2.500 HPS_DDR3_DQS_P[3]_OUT

Info (332111): 1000.000 HPS_I2C0_SCL

Info (332111): 1000.000 HPS_I2C1_SCL

Info (332111): 16.666 HPS_USB_CLK

Info (332111): 50.000 SD_SCLK

Info (332111): 2.500 soc_system:u0|soc_system_hps:hps|soc_system_hps_hps_io:hps_io|soc_system_hps_hps_io_border:border|hps_sdram:hps_sdram_inst|hps_sdram_pll:pll|afi_clk_write_clk

Info (332111): 2.500 soc_system:u0|soc_system_hps:hps|soc_system_hps_hps_io:hps_io|soc_system_hps_hps_io_border:border|hps_sdram:hps_sdram_inst|hps_sdram_pll:pll|pll_write_clk_dq_write_clk

Info (332111): 2.500 u0|hps|hps_io|border|hps_sdram_inst|hps_sdram_p0_sampling_clock

Info (332111): 3.333 u0|ks10|PLL|general[0].gpll~FRACTIONAL_PLL|vcoph[0]

Info (332111): 80.000 u0|ks10|PLL|general[0].gpll~PLL_OUTPUT_COUNTER|divclk

Info (332111): 80.000 u0|ks10|PLL|general[1].gpll~PLL_OUTPUT_COUNTER|divclk

Info (332111): 80.000 u0|ks10|PLL|general[2].gpll~PLL_OUTPUT_COUNTER|divclk

Info (332111): 80.000 u0|ks10|PLL|general[3].gpll~PLL_OUTPUT_COUNTER|divclk

Info (176233): Starting register packing

Info (176235): Finished register packing

Extra Info (176218): Packed 2 registers into blocks of type I/O output buffer

Extra Info (176220): Created 1 register duplicates

Warning (15705): Ignored locations or region assignments to the following nodes

Info (11798): Fitter preparation operations ending: elapsed time is 00:00:33

Info (170189): Fitter placement preparation operations beginning

Info (14951): The Fitter is using Advanced Physical Optimization.

Info (170190): Fitter placement preparation operations ending: elapsed time is 00:00:33

Info (170191): Fitter placement operations beginning

Info (170137): Fitter placement was successful

Info (170192): Fitter placement operations ending: elapsed time is 00:00:31

Info (170193): Fitter routing operations beginning

Info (170195): Router estimated average interconnect usage is 12% of the available device resources

Info (170196): Router estimated peak interconnect usage is 42% of the available device resources in the region that extends from location X33_Y23 to location X44_Y34

Info (170199): The Fitter performed an Auto Fit compilation. Optimizations were skipped to reduce compilation time.

Info (170201): Optimizations that may affect the design's routability were skipped

Info (170200): Optimizations that may affect the design's timing were skipped

Info (170194): Fitter routing operations ending: elapsed time is 00:00:50

Info (11888): Total time spent on timing analysis during the Fitter is 68.39 seconds.

Info (334003): Started post-fitting delay annotation

Info (334004): Delay annotation completed successfully

Info (334003): Started post-fitting delay annotation

Info (334004): Delay annotation completed successfully

Info (11801): Fitter post-fit operations ending: elapsed time is 00:00:46

Warning (171167): Found invalid Fitter assignments. See the Ignored Assignments panel in the Fitter Compilation Report for more information.

Warning (169064): Following 2 pins have no output enable or a GND or VCC output enable - later changes to this connectivity may change fitting results

Info (169065): Pin ESD_DIO has a permanently disabled output enable File: F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/de10_ks10.v Line: 161

Info (169186): Following groups of pins have the same dynamic on-chip termination control

Info (144001): Generated suppressed messages file F:/pdpx/pdp10/ks10/fpga/de10_top/quartus/output_files/de10_ks10.fit.smsg

Info: Quartus Prime Fitter was successful. 0 errors, 9 warnings

Info: Peak virtual memory: 9293 megabytes

Info: Processing ended: Sat Mar 05 04:23:28 2022

Info: Elapsed time: 00:04:48

Info: Total CPU time (on all processors): 00:23:08

/cygdrive/c/intelFPGA_lite/18.1/quartus/bin64/quartus_asm --read_settings_files=off --write_settings_files=off --rev=de10_ks10 de10_top/quartus/de10_ks10

Info: *******************************************************************

Info: Running Quartus Prime Assembler

Info: Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Info: Copyright (C) 2018 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the applicable agreement for further details.

Info: Processing started: Sat Mar 05 04:23:31 2022

Info: Command: quartus_asm --read_settings_files=off --write_settings_files=off --rev=de10_ks10 de10_top/quartus/de10_ks10

Info (115030): Assembler is generating device programming files

Info (11878): Hard Processor Subsystem configuration has not changed and a Preloader software update is not required

Info: Quartus Prime Assembler was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 5076 megabytes

Info: Processing ended: Sat Mar 05 04:23:48 2022

Info: Elapsed time: 00:00:17

Info: Total CPU time (on all processors): 00:00:17

/cygdrive/c/intelFPGA_lite/18.1/quartus/bin64/quartus_pgm --mode=jtag --operation=p\;de10_top/quartus/output_files/de10_ks10.sof"@2" --quiet

Info: *******************************************************************

Info: Running Quartus Prime Programmer

Info: Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition