REPORTE DE CÓDIGO FASE 2: INSTRUCCIONES TIPO I - AlexDominguez18/MIPS_32_BITS GitHub Wiki

INSTRUCCIONES TIPO I

Esta segunda fase se enfoca en las instrucciones de tipo I, es decir, las instrucciones inmediatas. Recordemos que la fase anterior se enfocaba en las instrucciones tipo R, así que ahora conoceremos e implementaremos las de tipo I, a continuación algunas características generales de las instrucciones de tipo I.

En las instrucciones de tipo I a grandes rasgos se llevan a cabo: La transferencia de datos, salto condicional e instrucciones con operandos inmediatos.

¿A qué se refiere salto condicional?

Esto se refiere al momento o punto tal que dentro de un programa su flujo se ve alterado, es decir, tiende hacia otra dirección. Una instrucción que causa un salto puede ser efectiva o no efectiva. Si el salto no es efectivo el flujo del programa no cambia y la siguiente instrucción que se ejecutará será la que está inmediatamente después, según el código. En otro caso, si el salto resulta efectivo la siguiente instrucción ejecutada será aquella que está marcada como destino del salto.

¿A qué se refiere operandos inmediatos?

Una instrucción de tipo inmediato tiene un campo de operando en vez de un campo de dirección. El campo del operando contiene el operando actual que se debe utilizar en conjunto con la operación especificada en la instrucción. Es decir, en estas instrucciones el operando es especificado en la instrucción misma.

Las instrucciones de modo inmediato son útiles para inicializar los registros en un valor constante. Las desventajas principales son que el valor del dato es constante y el rango de valores que se pueden representar está limitado por el tamaño de este operando.

INSTRUCCIONES

Tipo R

Add : Lo que hace esta instrucción es que al valor de la palabra rt se agrega el valor de rs produciendo un resultado que se guarda en rd.

Add $rd, $rs, $rt.

Sub : Al contrario de la instrucción anterior, esta se enfoca en restar. El valor de la palabra de rt se resta del valor de rs para producir un resultado que se almacena en rd.

Sub $rd, $rs, $rt.

Mul : En esta instrucción el valor en rs se multiplica por el valor en rt escribiendo los bits menos significativos en rd.

Mul $rd, $rs, $rt.

Div : Esta instrucción divide el valor de las palabras, tratando los operandos como valores con signo. El valor en rs se divide por el valor de rt.

Div $rd, $rs, $rt.

Or : Esta instrucción es la operación lógica OR. Por lo que el valor de rs se combina con el contenido de rt en una operación OR lógica a nivel de bit. El resultado es colocado en rd.

Or $rd, $rs, $rt.

And : Al igual que la instrucción anterior se trata de una operación lógica, AND. El contenido de rs se combina con el contenido de rt en una operación AND lógica a nivel de bit. El resultado es colocado en rd.

And $rd, $rs, $rt.

Subu : Al igual que "Sub" esta instrucción resta, solo que en este caso resta palabras sin signo.

Subu $rd, $rs, $rt.

Xor : Otra de las operaciones lógicas, esta la Xor. Combina el contenido en rs y rt en una operacion logica xor y coloca el resultado en rd.

Xor $rd, $rs, $rt.

Slt : Esta es una instrucción que compara. Compara el contenido de rs y rt como enteros con signo y coloca el resultado de la comparación en rd. Si el rs es menor que el rt, el resultado es 1 (verdadero). De lo contrario, es 0 (falso).

Slt $rd, $rs, $rt.

Nor : Otra operación lógica más, esta es la Not or. El contenido del rs se combina con el contenido de rt en una operación lógica de bits NOR. El resultado es colocado en rd.

Nor $rd, $rs, $rt.

Nop : Esta instrucción no realiza ninguna operación. En el lenguaje ensamblador "Nop" es utilizado para denotar no operación.

Nop

Tipo I

Addi : Add inmediata. Añade una palabra inmediata. El valor inmediato con signo se suma al valor de rs para producir un resultado que se coloca en rd (siempre y cuando la suma no se desborde).

Addi $rt, $rs, $inmediate.

Ori : Or inmediata. El valor inmediato es cero extendido a la izquierda y combinado con el contenido de rs en un una operación lógica a bit Or. El resultado se coloca en rt.

Ori $rt, $rs, $inmediate.

Andi : And inmediata. El valor inmediato es cero extendido a la izquierda y combinado con el contenido de rs en una operación lógica a bit And. El resultado se coloca en rt.

Andi $rt, $rs, $inmediate.

Lw : Esta instrucción carga una palabra con signo de la memoria. El contenido de la palabra en el lugar de memoria especificado por la dirección se obtiene, se extiende hasta la longitud de registro del GPR si es necesario, y se coloca en rt.

Lw $rt, $offset.

Slti : Es slt inmediata. Compara el contenido de rs y de inmediato y registra el resultado de la comparacion en rt. Si rs es menor a inmediato el resultado es 1 (verdadero) de lo contrario es 0 (falso).

Slti $rt, $rs, $inmediate.

Beq : Esta es también una instrucción de comparación. Branch on equal BEQ. Se añade un offset de 18 bits (el campo de offset de 16 bits desplazado a la izquierda 2 bits) a la dirección de la instrucción que sigue a la rama (no la rama misma), para formar una dirección de destino efectiva con el PC. Si el contenido de rs y rt es igual, se bifurca a la dirección de destino efectiva.

Beq $rt, $offset.

Bgtz : Similar a Beq. Se añade un offset de 18 bits (el campo de desplazamiento de 16 bits se desplaza a la izquierda 2 bits) a la dirección de la instrucción que sigue a la rama (no la rama misma), para formar una dirección de destino efectiva relacionada con el PC. Si el contenido de rs es mayor a cero, se bifurca a la dirección de destino efectiva.

Bgtz $rt, $offset.

Bne : Branch on not equal. Se añade un offset de 18 bits (el campo de desplazamiento de 16 bits se desplaza a la izquierda 2 bits) a la dirección de la instrucción que sigue a la rama (no la rama misma), para formar una dirección de destino efectiva relacionada con el PC. Si el contenido de rs y rt no es igual, se bifurca a la dirección de destino efectiva.

Bne $rt, $offset.

Lb : Carga un byte de la memoria como un valor con signo. El contenido del byte de 8 bits en la ubicación de memoria especificada se carga, con signo, y se coloca en rt. El offset de 16 bits se añade al contenido de la base para formar la dirección efectiva.

Lb $rt, $offset.

Tipo J

J : Esta instrucción es Jump, salto. Los 28 bits de la dirección del objetivo es el campo instr_index desplazado a la izquierda 2 bits. Los restantes bits son los correspondientes a la dirección de la instrucción. Salta a la dirección de destino efectiva. Antes de ejecutar el salto ejecuta la instrucción que sigue al salto.

J target.

Jr : Jump register, registro de saltos. Esta instrucción salta a la dirección correspondiente en rs. Y ejecuta la instrucción después del salto.

Jr $rs.

OBJETIVO

El objetivo de esta fase es lograr implementar los módulos del MIPS necesarios para poder llevar a cabo la ejecución de las instrucciones de Tipo I. En la fase anterior implementamos todos los módulos, solo faltaría adecuarlos para ejecutar instrucciones tipo I.

Los modelos en el cual nos basaremos para llevar a cabo esta fase son las siguientes imágenes:

Aquí se resaltan los módulos que se usan para ejecutar la instrucción Lw

Aquí se resaltan los módulos que se usan para ejecutar la instrucción Beq

DESARROLLO

Unidad de Control

Se agregaron más Opcodes a la unidad de control para que se puedan ejecutar más instrucciones.

El Control de la ALU

Se cambió el ALUOp de 2 a 3 bits para poder hacer uso de más instrucciones. En la siguiente tabla se muestra que operación de la ALU utiliza cada instrucción;

Memoria de Datos

Esta recibe el resultado de la ALU en Dirección y El Read Data2 del BR en el Dato a Escribir. La memoria de datos Lee o Escribe según como le indique el Control, esta no puede hacer ambas al mismo tiempo como en Banco de Registros. En la instrucción Lw Lee y en la Sw Escribe.

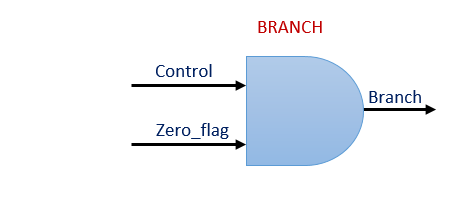

Branch

El branch se usa en la instrucción BEQ, el cual funciona con una AND, el control le manda un 1 si es la instrucción BEQ en la primera entrada y en la otra si se activa el zeroflag (es decir si rs y rt son iguales). Y así cuando las dos entradas de la AND son 1 el branch se activa.

Pruebas del funcionamiento de la segunda fase:

Una vez realizados algunos cambios a los módulos necesarios para llevar a cabo la ejecución de las instrucciones tipo I. Se procedió a verificar que nuestro MIPS fuera capaz de ejecutar las siguientes instrucciones.

Se realizarán las siguientes 7 operaciones:

- Addi $0, $8, #10

- Slti $0, $9, #10

- Andi $0, $10, #10

- Ori $0, $11, #10

- Sw $0, $8, #0

- Lw $0, $12, #0

- Beq $0, $0, #65520

Tras la ejecución de las instrucciones, se guardaron los siguientes resultados en el banco de registros:

Tal y como indicaba la instrucción sw $0, $8, #10. Se está guardando un 10 en el registro 0 de la memoria de datos.

RESULTADO DEL BRANCH Podemos observar como el Branch se activa en el ns 200 y finaliza en el 220. Esto porque realizó la comparación entre 0 y 0, activando el zero flag y de esta manera se activa la compuerta AND del Branch.

Al ejecutarse el Branch, saltamos a la primera instrucción