# AUTOMOTIVE SOFTWARE ENGINEERING

## PRINCIPLES, PROCESSES, METHODS, AND TOOLS

Jörg Schäuffele Thomas Zurawka

Translated by Roger Carey

Warrendale, Pa.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of SAE.

For permission and licensing requests, contact: SAE Permissions 400 Commonwealth Drive Warrendale, PA 15096-0001 USA E-mail: permissions@sae.org Tel: 724-772-4028 Fax: 724-772-4891

| Library of Congress Cataloging-in-Publication Data                    |

|-----------------------------------------------------------------------|

| Schäuffele, Jörg.                                                     |

| [Automotive software engineering. English]                            |

| Automotive software engineering: principles, processes, methods, and  |

| tools / Jörg Schäuffele, Thomas Zurawka ; translated by Roger Carey.  |

| p. cm.                                                                |

| Translation from the German language ed.                              |

| Includes bibliographical references and index.                        |

| ISBN-10 0-7680-1490-5                                                 |

| ISBN-13 978-0-7680-1490-5                                             |

| 1. Automotive computers. 2. Software engineering. I. Zurawka, Thomas. |

| II. Title.                                                            |

| TL272.53.S33 2005                                                     |

Translated from the German language edition:

Automotive Software Engineering: Grundlagen, Prozesse, Methoden und Werkzeuge by Jörg Schäuffele and Thomas Zurawka Copyright © Friedr. Vieweg & Sohn Verlag/GWV Fachverlage GmbH, Wiesbaden, Germany, 2003 ISBN 3-528-01040-1

SAE International 400 Commonwealth Drive Warrendale, PA 15096-0001 USA E-mail: CustomerService@sae.org Tel: 877-606-7323 (inside USA and Canada) 724-776-4970 (outside USA) Fax: 724-776-1615

Copyright © 2005 SAE International ISBN-10 0-7680-1490-5 ISBN-13 978-0-7680-1490-5 SAE Order No. R-361 Printed in the United States of America.

## THE ROLE OF SOFTWARE IN THE AUTOMOBILE

## Managing complexity is possible only through new approaches to development.

No other technology offers developers as high a degree of design freedom as software technology does. The almost exponential growth of software in the vehicle is driven by an increase in vehicle functions and networks of functions, stringent reliability and safety requirements, as well as an increasing number of vehicle variants. Managing the resulting complexity poses a great challenge to both vehicle manufacturers and their suppliers: They must reduce software complexity to a minimum by using methodology in development that ensures the safe functioning of software and systems. This book proffers a host of ideas for the design of development processes and for the effective application of methods and tools.

Dr. Siegfried Dais, Deputy Chairman, Board of Management, Robert Bosch GmbH, Stuttgart, Germany

## Software in the vehicle is becoming a strategic product.

For vehicle manufacturers, software in the vehicle is evolving into a product of increased strategic value. Electronics and software in the vehicle have become an essential impetus for innovation—about 90% of innovations in the vehicle today are driven by electronics. On the one hand, more and more of the classic vehicle functions are being realized by means of software; on the other hand, entirely new opportunities are created by networking functions that formerly used to be independent of each other. Consistent application of systems engineering methods is a crucial factor for success in managing the vehicle as a complete system. This book addresses this extensive topic with special emphasis on the major vehicle subsystems of powertrain, chassis, and body.

Hans-Georg Frischkorn, Senior Vice President System Architecture and Integration, BMW Group, Munich, Germany

### From cost driver to competitive advantage.

Only a pioneer in software technology will gain technological advantage in the automotive industry. Successful cooperation between engineers from various disciplines in systems engineering, however, will be possible only if everyone shares the same background knowledge, the same terminology, and an appropriate process model. This book uses real-life examples in an impressive demonstration of software engineering essentials and applicable methods.

Dr.-Ing. Wolfgang Runge, Member, Board of Management, ZF Lenksysteme GmbH, Schwäbisch Gmünd, Germany

### Embedded systems are an automotive asset.

Embedded computer systems provide opportunities to distinguish transportation products and services in the increasingly competitive automotive business. To interpret Moore's Law, electronics continue to become more powerful while prices keep dropping. The resulting systems complexity can be managed only with an in-depth understanding of the principles, practices, methods, and tools discussed in this essential text.

I applaud Dr. Zurawka and Mr. Schäuffele of ETAS GmbH on their comprehensive work on very important topics. This material must be understood by any organization wishing to participate in the automotive business. As we continue to evolve our engineering processes, I look forward to more assistance from the leaders in this field.

Craig A. Brown, GM Powertrain Engineering, General Motors Corp., Detroit, MI

## Advanced education—an opportunity and a challenge.

In the greater Stuttgart area, vehicle manufacturing is the preeminent industry, with development centers of major vehicle manufacturers and suppliers offering a great many job opportunities. At the University of Stuttgart, courses in software technology are part and parcel of the engineering program. This book offers students who are pursuing an academic degree in engineering the opportunity to familiarize themselves with practical automotive industry applications. In fact, the methods introduced in this book may even serve as models for applications in other industries.

*Prof. Dr.-Ing. Dr. h.c. Peter Göhner, Institute for Automation and Software Technology, University of Stuttgart, Germany*

## Vehicle development needs perspective based on integrated model.

As a natural consequence of ongoing advances in vehicle development, customer expectations must be satisfied while ensuring compliance with government regulations. Increasingly, these and related areas are the special domain of automotive electronic systems.

In fact, most of the competitive advantage in vehicles today tends to lie in the electronic content of the vehicle, the software component being a major part of these systems. The safe, reliable, cost effective, and rapid development of automotive software-based systems are major issues for vehicle and component manufacturers. Authors Schäuffele and Zurawka address the complex issues of automotive electronic systems development from a perspective based on an integrated model, offering students a paradigm for an integrated systems solution to vehicle embedded software engineering. The book will serve as a foundation for integrated vehicle software development practices as this technology continues to emerge and expand.

Prof. Mark Thompson, Electrical and Computer Engineering, Kettering University, Flint, MI

### A new system science is needed.

As hardware development costs and manufacturing fixed costs have been increasing dramatically and as product requirements change faster and faster over a short period of time, embedded system, subsystem and even IC designers have turned to software as a way of coping with these problems. Yet this shift has caused an entire new set of challenges. Software programs have not been born equal. Software for transportation systems for example has to satisfy hard constraints that depend on the implementation platform thus making the very base of the traditional software abstraction invalid. It is no wonder that more than 30% of severe malfunctions in automobiles are originated by faulty software. We need a new system science to deal with the digital abstraction and the physical world in a unified way. This book is the documentation of pioneering work carried out by the authors in developing *methodologies* and tools for automotive software. The importance of methodologies cannot be overemphasized as tool power can only be unleashed by appropriate methodologies as I have learned over the years in my work in EDA. The unique value of this book is in documenting the effort of conjugating methodologies and tools, a very successful one indeed as the prosperity of ETAS witnesses.

Prof. Alberto Sangiovanni Vincentelli, The Edgar L. and Harold H. Buttner Chair of EECS, University of California at Berkeley; Co-founder, Chief Technology Advisor and Member of the Board of Directors, Cadence Design Systems, Berkeley, CA

## ACKNOWLEDGMENTS

We would like to take this opportunity to express to all of our customers our appreciation for the many years of successful and trusting cooperation. This book would not have been possible without this valuable exchange of experiences.

We also wish to thank the BMW Group for its kind permission to include experiences gathered while working on proprietary BMW projects—in the case of one author (Jörg Schäuffele), also in his capacity as an employee at BMW. This includes the consideration of process definitions, as well as recommendations for production projects at BMW. We are indebted to Hans-Georg Frischkorn for his foreword to this book, and special thanks go to Heinz Merkle, Dr. Helmut Hochschwarzer, Dr. Maximilian Fuchs, Prof. Dr. Dieter Nazareth, and all of their staff.

Many of the processes and methods presented in this book evolved over many years of trusting cooperation with Robert Bosch GmbH. These processes and methods are now widely accepted, and they keep recurring here and there throughout this book. We gratefully acknowledge the valuable input from the capable staff in the Chassis Systems, Diesel Systems, and Gasoline Systems Divisions, and the Research and Advanced Development Department of Robert Bosch GmbH.

Sincere thanks also go to Dr. Siegfried Dais, Dr. Wolfgang Runge, Craig A. Brown, Prof. Dr. Peter Göhner, Prof. Mark Thompson, and Prof. Alberto Sangiovanni Vincentelli for their words in the foreword section titled "The Role of Software in the Automobile."

We also are indebted to our many colleagues who, over these past years, have contributed to this book in many different ways.

For the careful and critical task of copy-editing the manuscript, we express our sincere appreciation to Roland Jeutter, Dr. Michael Nicolaou, Dr. Oliver Schlüter, Dr. Kai Werther, and Hans-Jörg Wolff.

Finally, for the careful English translation of the manuscript, sincere thanks go to Roger Carey.

Jörg Schäuffele Thomas Zurawka Stuttgart, Germany June 2005

## PREFACE

After a history of more than 100 years, the automobile as a product continues to evolve at a very fast pace. Since the early 1970s, its evolution has strongly been influenced by a steady increase in onboard electronic systems and software in the vehicle—a trend that continues unabated. As a consequence of this trend, vehicle development, production, and service are changing in fundamental ways. Using software to implement functions in the vehicle provides developers with new degrees of freedom and solutions to existing conflicts of objectives. The resulting complexity can be managed only by using processes, methods, and tools that are appropriate for vehicle-specific applications.

In the last few years, various methods and standards have been devised for the development of software for in-vehicle electronic systems. These methods and standards are best described by the collective term *automotive software engineering*.

Over time, a complex terminology has evolved in automotive software engineering. All of us working in this field are confronting these terms on a daily basis. However, it is no overstatement to say that many of us are no longer sure of a clear or shared definition of many of these terms. In fact, some of the terms are used in very different contexts where they clearly do not mean one and the same thing. For example, the term "process" occurs not only in the context of control engineering but is also used (to designate a very specific thing) in conjunction with real-time systems—to say nothing of its general meaning in development, where it describes development methods in a wider context. In this book, we define essential terms and then use them consistently as defined.

The chapters of this book focus on the processes, methods, and tools for the development of software for electronic systems in the vehicle. The book also places emphasis on the interaction between software development (as a professional discipline limiting itself to certain vehicle components) and the all-embracing systems engineering (a field that considers all vehicle components). The development methods introduced—the so-called *processes*—take the form of models, that is, they comprise an abstract and idealized reflection of daily practice. Although they may serve as guidelines for a variety of development projects, they will need to be evaluated and adapted before they are applied to specific projects. We have taken great pains to provide clear and unambiguous descriptions of processes and supporting methods and tools.

The wealth of information available on many aspects of our topic forced us to forgo detailed discussion of some of them. Generally speaking, we have limited our discussion to aspects that are relevant and specific to the automotive industry.

We certainly make no claim of having provided here the only proper or even a complete methodological approach. As employees of ETAS, we are convinced, however, that tools and software components by ETAS are ideally suited to support the processes and methods introduced in this book.

## **Practical Cases in Point**

To a development team, a process serves only as a supporting structure. The introduction of any given process will be successful only if every team member sees it as a benefit. When extensive practical tasks and their solutions can be made transparent to everyone in the team because every activity associated with any given task can be traced, this is a benefit. In this sense, this book is not a theoretical textbook, far removed from the practical world. On the contrary, all of its ideas, concepts, and suggestions are based on practical use cases that we present by means of appropriate examples. Of course, these aspects are derived from the experience we gained over the years while working closely with vehicle manufacturers and suppliers. Examples come from production projects, including associated service considerations, as well as from research and advanced development projects.

## **Readership of This Book**

We would like to offer this book to all who work for manufacturers and suppliers in vehicle development, production, and service and who encounter software in the vehicle during their daily activities. We hope to be able to pass on some useful suggestions.

In addition, we hope this book will serve as a basic tool for the instruction of engineering students and for the introduction of new employees to their respective workplaces. Basic familiarity with open-loop and closed-loop control engineering, system theory, and software engineering, although helpful, is not a prerequisite for being able to understand the topic of this book.

Readers may feel in some places that they could benefit from more detailed discussion of one topic or another. If you are one of these readers, please let us know. We welcome any and all feedback and especially any suggestions for improvement, which we will carefully consider for inclusion in subsequent reprintings.

## TABLE OF CONTENTS

| 1. | Intro | duction | and Overview                                                  | 1  |

|----|-------|---------|---------------------------------------------------------------|----|

|    | 1.1   | The Dr  | river-Vehicle-Environment System                              | 2  |

|    |       | 1.1.1   | Design and Method of Operation of Vehicle Electronic Systems  | 2  |

|    |       | 1.1.2   | Electronic Systems of the Vehicle and the Environment         | 5  |

|    | 1.2   | Overvi  | ew of Vehicle Electronic Systems                              | 6  |

|    |       | 1.2.1   | Electronic Systems of the Powertrain                          |    |

|    |       |         | 1.2.1.1 User Interfaces and Setpoint Generators               | 8  |

|    |       |         | 1.2.1.2 Sensors and Actuators                                 | 9  |

|    |       |         | 1.2.1.3 Software Functions                                    | 9  |

|    |       |         | 1.2.1.4 Installation Space                                    | 10 |

|    |       |         | 1.2.1.5 Variants and Scalability                              | 10 |

|    |       | 1.2.2   | Electronic Systems of the Chassis                             |    |

|    |       |         | 1.2.2.1 User Interfaces and Setpoint Generators               | 11 |

|    |       |         | 1.2.2.2 Sensors and Actuators                                 | 11 |

|    |       |         | 1.2.2.3 Software Functions                                    | 11 |

|    |       |         | 1.2.2.4 Installation Space                                    | 12 |

|    |       |         | 1.2.2.5 Variants and Scalability                              | 12 |

|    |       | 1.2.3   | Body Electronics                                              | 12 |

|    |       |         | 1.2.3.1 User Interfaces and Setpoint Generators               | 13 |

|    |       |         | 1.2.3.2 Sensors and Actuators                                 | 13 |

|    |       |         | 1.2.3.3 Software Functions                                    |    |

|    |       |         | 1.2.3.4 Installation Space                                    |    |

|    |       |         | 1.2.3.5 Variants and Scalability                              |    |

|    |       | 1.2.4   | Multimedia Systems                                            |    |

|    |       | 1.2.5   | Distributed and Networked Electronic Systems                  |    |

|    |       | 1.2.6   | Summary and Outlook                                           |    |

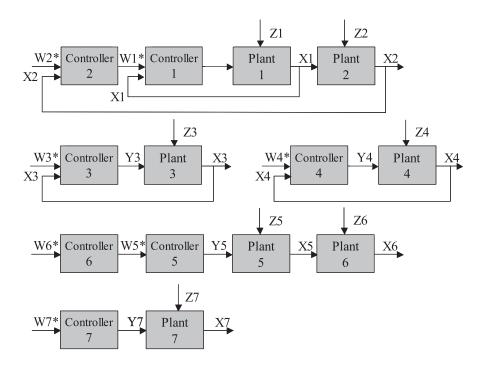

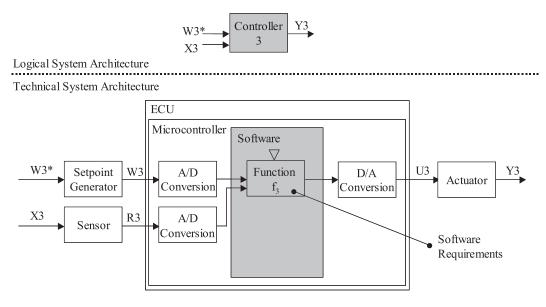

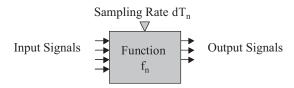

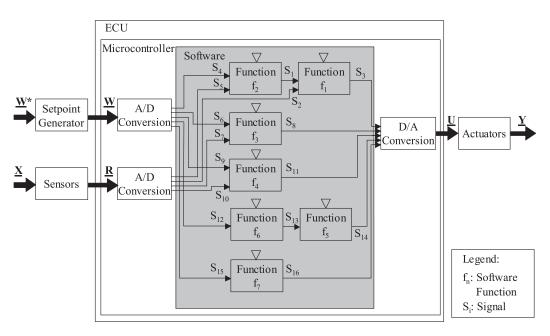

|    | 1.3   | Overvi  | ew of the Logical System Architecture                         |    |

|    |       | 1.3.1   | ECU and Function Networks of the Vehicle                      | 17 |

|    |       | 1.3.2   | Logical System Architecture for Open-Loop/Closed-Loop Control |    |

|    |       |         | and Monitoring Systems                                        |    |

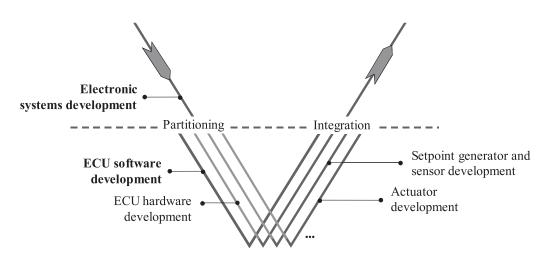

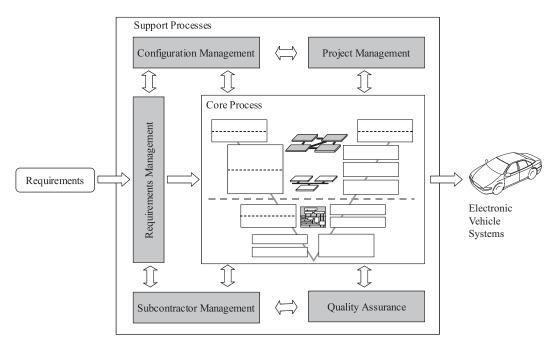

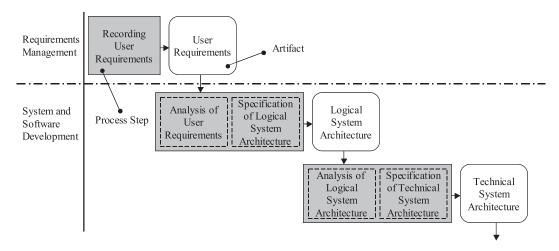

|    | 1.4   | Proces  | ses in Vehicle Development                                    |    |

|    |       | 1.4.1   | Overview of Vehicle Development                               |    |

|    |       | 1.4.2   | Overview of the Development of Electronic Systems             |    |

|    |       |         | 1.4.2.1 Trend from Hardware to Software                       |    |

|    |       |         | 1.4.2.2 Cost                                                  |    |

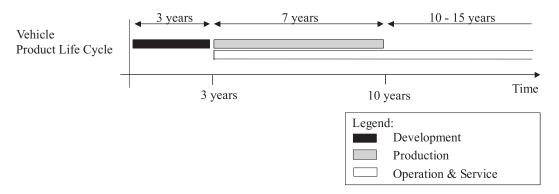

|    |       |         | 1.4.2.3 Long Product Life Cycles                              |    |

|    |       |         | 1.4.2.4 Safety Requirements—High and Still Rising             | 23 |

|    |       |         |                                                               |    |

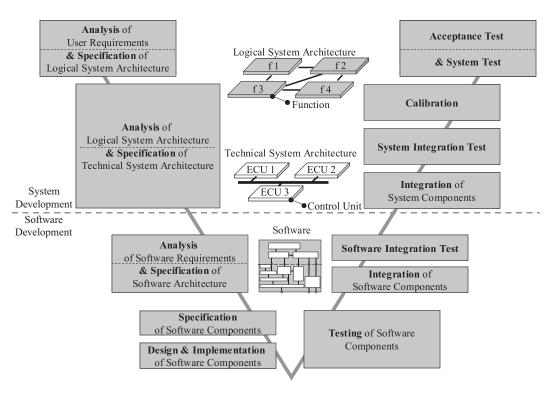

|    |       | 1.4.3<br>1.4.4 | Core Process for Electronic Systems and Software Development<br>Support Processes for Electronic Systems and Software | 23 |

|----|-------|----------------|-----------------------------------------------------------------------------------------------------------------------|----|

|    |       |                | Development                                                                                                           | 26 |

|    |       |                | 1.4.4.1 Customer/Supplier Relationships                                                                               |    |

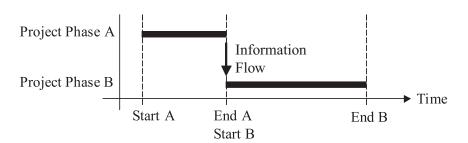

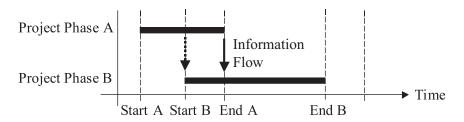

|    |       |                | 1.4.4.2 Simultaneous Engineering and Different Development                                                            |    |

|    |       |                | Environments                                                                                                          |    |

|    |       | 1.4.5          | Production and Service of Electronic Systems and Software                                                             |    |

|    | 1.5   | Method         | ls and Tools for the Development of Software for Electronic Systems                                                   |    |

|    |       | 1.5.1          | Model-Based Development                                                                                               |    |

|    |       | 1.5.2          | Integrated Quality Management                                                                                         |    |

|    |       |                | 1.5.2.1 Quality Assurance Guidelines                                                                                  |    |

|    |       |                | 1.5.2.2 Quality Control, Validation, and Verification Measures                                                        |    |

|    |       | 1.5.3          | Reducing the Development Risk                                                                                         |    |

|    |       | 11010          | 1.5.3.1 Early Validation of Software Functions                                                                        |    |

|    |       |                | 1.5.3.2 Reuse of Software Functions                                                                                   |    |

|    |       | 1.5.4          | Standardization and Automation                                                                                        |    |

|    |       | 1.0.1          | 1.5.4.1 Standardization                                                                                               |    |

|    |       |                | 1.5.4.2 Automation                                                                                                    |    |

|    |       | 1.5.5          | Development Steps in the Vehicle                                                                                      |    |

|    |       | 1.0.0          |                                                                                                                       | 50 |

| 2. | Esser | ntial Sys      | stem Basics                                                                                                           | 39 |

|    | 2.1   | Open-L         | Loop and Closed-Loop Control Systems                                                                                  |    |

|    |       | 2.1.1          | Modeling                                                                                                              | 40 |

|    |       | 2.1.2          | Block Diagrams                                                                                                        | 40 |

|    | 2.2   | Discret        | e Systems                                                                                                             | 44 |

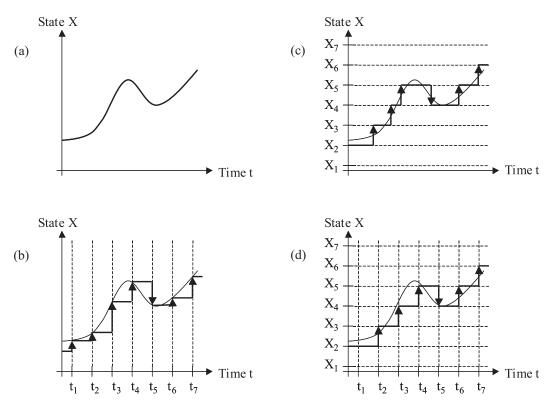

|    |       | 2.2.1          | Time-Discrete Systems and Signals                                                                                     | 46 |

|    |       | 2.2.2          | Value-Discrete Systems and Signals                                                                                    | 47 |

|    |       | 2.2.3          | Time- and Value-Discrete Systems and Signals                                                                          | 48 |

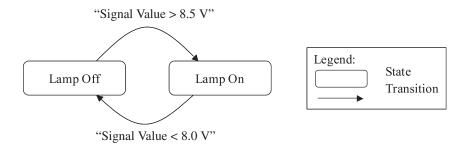

|    |       | 2.2.4          | State Machines                                                                                                        | 48 |

|    | 2.3   | Embed          | ded Systems                                                                                                           | 51 |

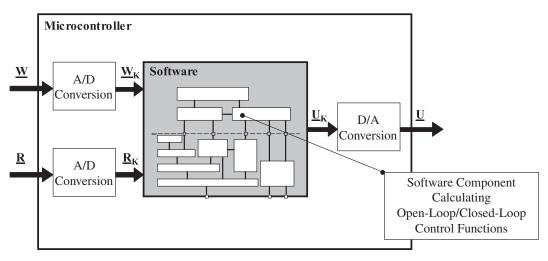

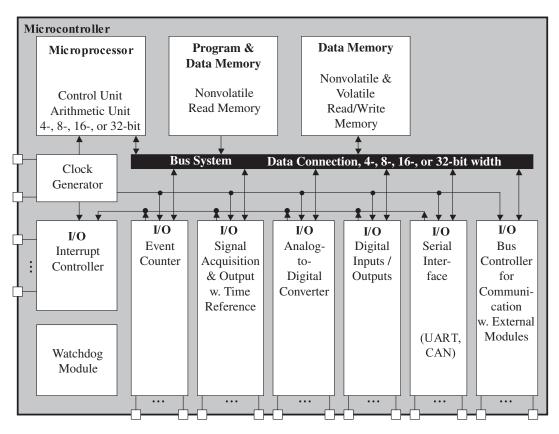

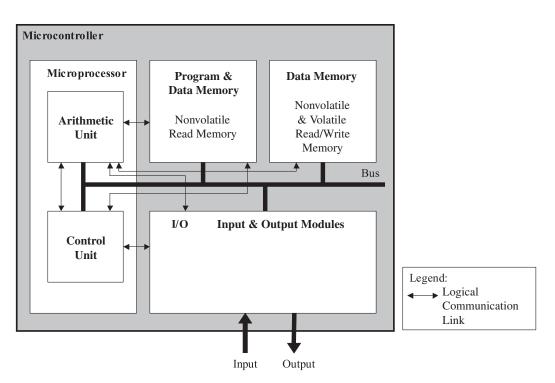

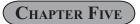

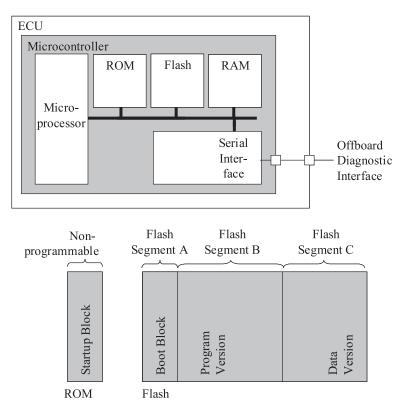

|    |       | 2.3.1          | Microcontroller Construction                                                                                          | 52 |

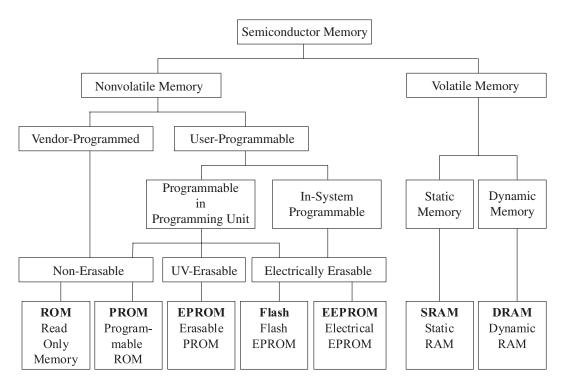

|    |       | 2.3.2          | Memory Technologies                                                                                                   | 54 |

|    |       |                | 2.3.2.1 Read/Write Memory                                                                                             | 54 |

|    |       |                | 2.3.2.2 Non-Erasable Read-Only Memory                                                                                 | 55 |

|    |       |                | 2.3.2.3 Reprogrammable Nonvolatile Memory                                                                             | 56 |

|    |       | 2.3.3          | Microcontroller Programming                                                                                           |    |

|    |       |                | 2.3.3.1 Program Version and Data Version                                                                              | 57 |

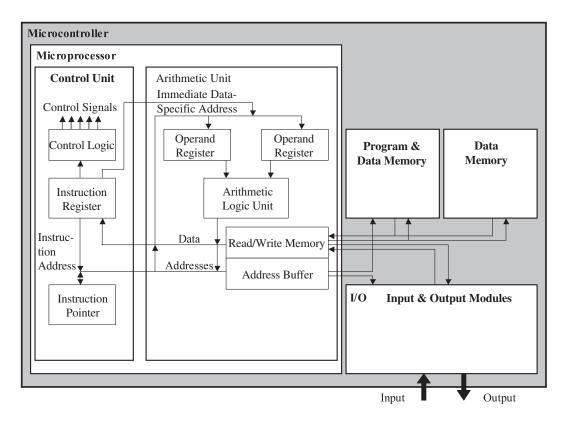

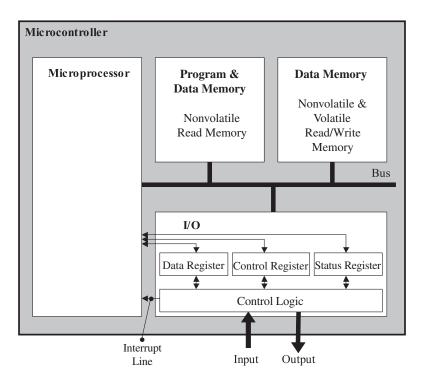

|    |       |                | 2.3.3.2 Functional Principles of Microcontrollers                                                                     |    |

|    |       |                | 2.3.3.3 Principal Microcontroller Operations                                                                          |    |

|    |       |                | 2.3.3.4 Microprocessor Architecture and Instruction Set                                                               |    |

|    |       |                | 2.3.3.5 I/O Module Architecture                                                                                       |    |

|    | 2.4   | Real-Ti        | ime Systems                                                                                                           |    |

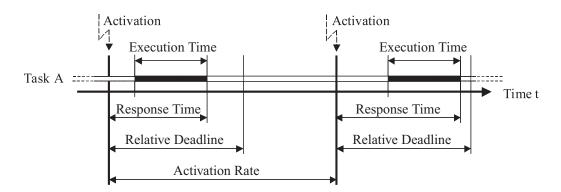

|    |       | 2.4.1          | Defining Tasks                                                                                                        |    |

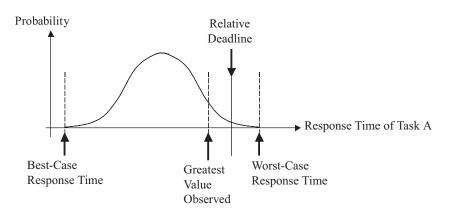

|    |       | 2.4.2          | Defining Real-Time Requirements                                                                                       |    |

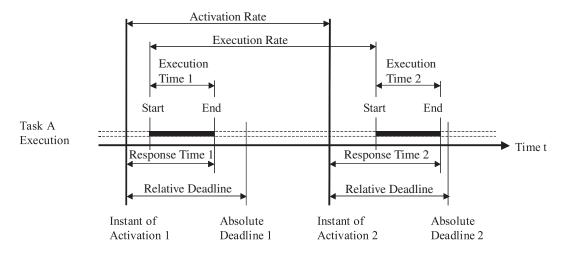

|    |       |                | 2.4.2.1 Instants of Task Activation and Task Deadline                                                                 |    |

|    |       |                | 2.4.2.2 Hard and Soft Real-Time Requirements                                                                          |    |

|    |       |                | - I.                                                                                                                  |    |

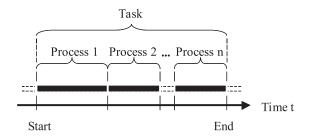

|     |         | 2.4.2.3 Defining Processes                                         | 69  |

|-----|---------|--------------------------------------------------------------------|-----|

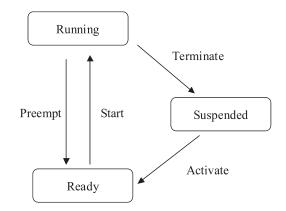

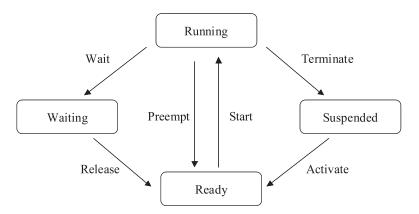

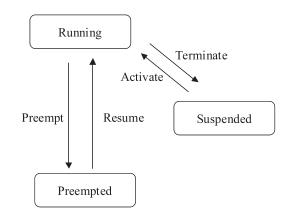

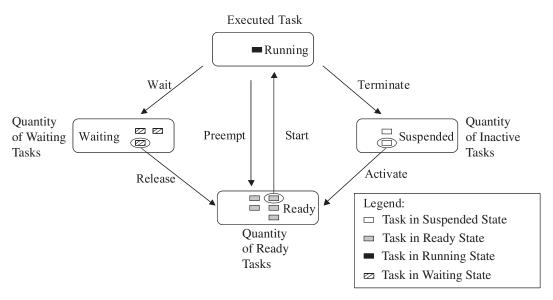

|     | 2.4.3   | Task States                                                        | 69  |

|     |         | 2.4.3.1 Basic Task State Model (per OSEK-OS)                       | 69  |

|     |         | 2.4.3.2 Extended Task State Model (per OSEK-OS)                    | 70  |

|     |         | 2.4.3.3 Task State Model (per OSEK-TIME)                           |     |

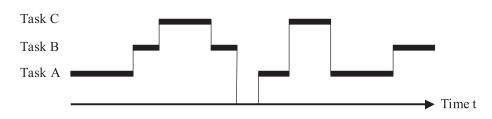

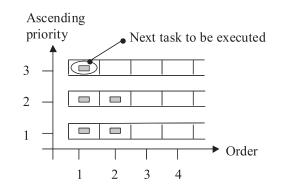

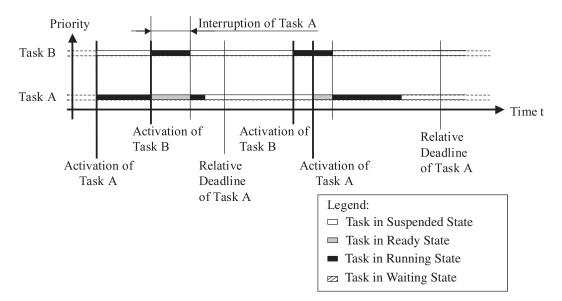

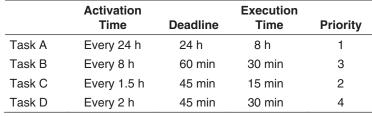

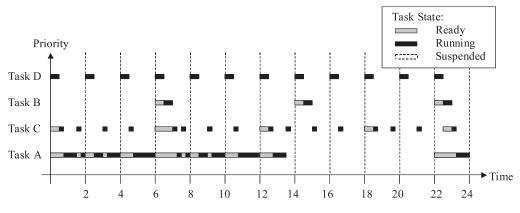

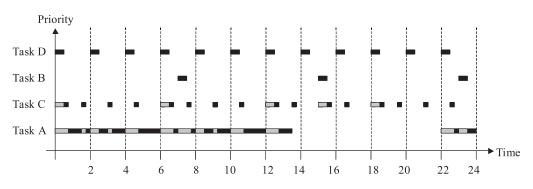

|     | 2.4.4   | Strategies for Processor Scheduling                                | 71  |

|     |         | 2.4.4.1 Processor Scheduling—In Sequential Order                   | 72  |

|     |         | 2.4.4.2 Processor Scheduling—By Priority                           | 72  |

|     |         | 2.4.4.3 Processor Scheduling—Combined Sequential and Priority      |     |

|     |         | Strategy                                                           | 73  |

|     |         | 2.4.4.4 Processor Scheduling—Preemptive Strategy                   | 74  |

|     |         | 2.4.4.5 Processor Scheduling—Nonpreemptive Strategy                | 74  |

|     |         | 2.4.4.6 Processor Scheduling—Event-Driven and Time-Controlled      |     |

|     |         | Strategies                                                         | 75  |

|     | 2.4.5   | Organization of Real-Time Operating Systems                        | 77  |

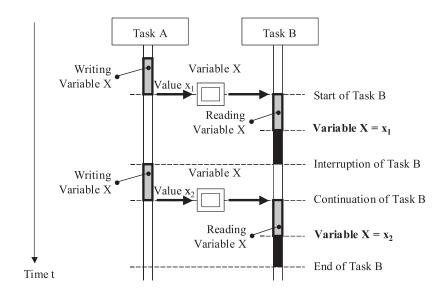

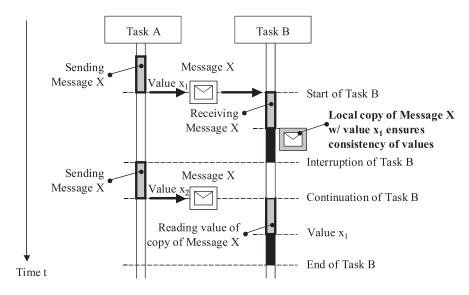

|     | 2.4.6   | Interaction Among Tasks                                            | 78  |

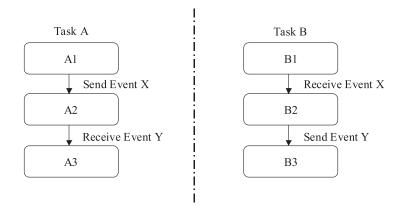

|     |         | 2.4.6.1 Synchronization                                            | 78  |

|     |         | 2.4.6.2 Cooperation                                                | 79  |

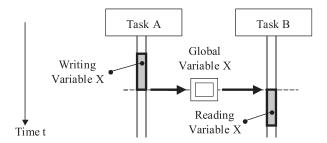

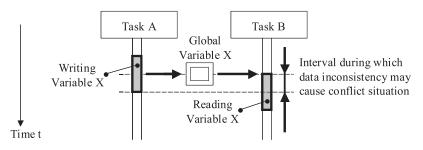

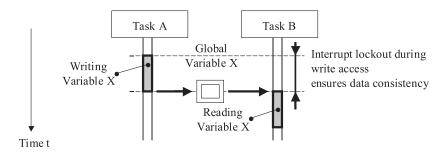

|     |         | 2.4.6.3 Communication                                              | 82  |

|     |         | 2.4.6.4 Interaction Among Tasks in the Logical System Architecture | 83  |

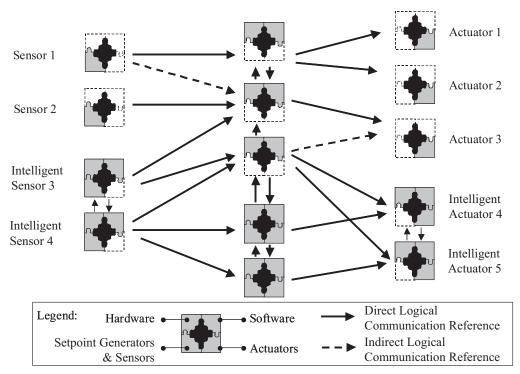

| 2.5 | Distrib | uted and Networked Systems                                         | 84  |

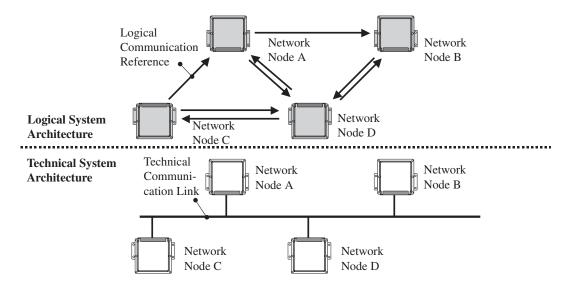

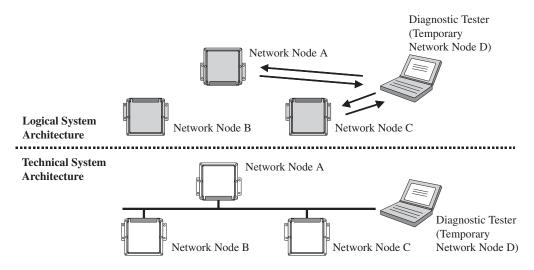

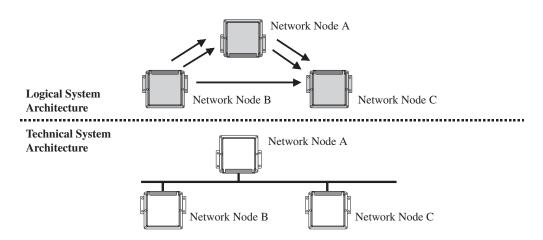

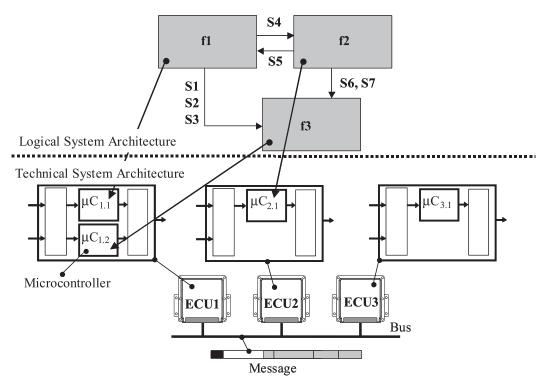

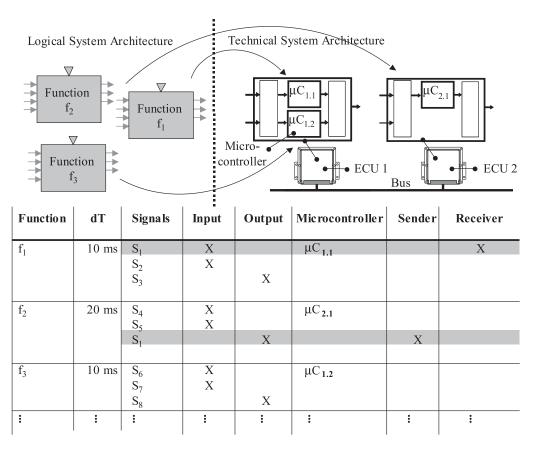

|     | 2.5.1   | Logical and Technical System Architecture                          | 87  |

|     | 2.5.2   | Defining Logical Communication Links                               | 88  |

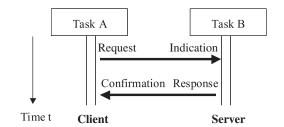

|     |         | 2.5.2.1 Client/Server Model                                        | 88  |

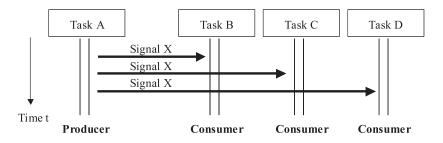

|     |         | 2.5.2.2 Producer/Consumer Model                                    | 89  |

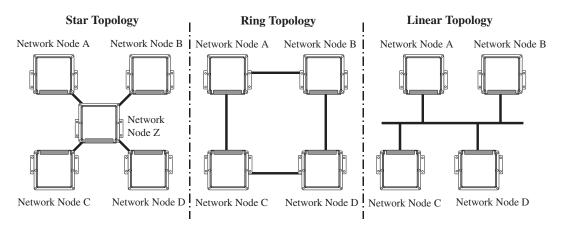

|     | 2.5.3   | Defining the Technical Network Topology                            | 90  |

|     |         | 2.5.3.1 Star Topology                                              |     |

|     |         | 2.5.3.2 Ring Topology                                              | 91  |

|     |         | 2.5.3.3 Linear Topology                                            | 91  |

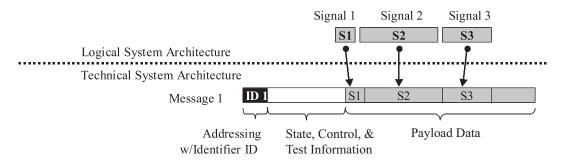

|     | 2.5.4   | Defining Messages                                                  | 91  |

|     |         | 2.5.4.1 Addressing                                                 | 92  |

|     |         | 2.5.4.2 Communications Matrix                                      |     |

|     | 2.5.5   | Organization of Communications and Network Management              | 94  |

|     |         | 2.5.5.1 Communications (per OSEK-COM)                              |     |

|     |         | 2.5.5.2 Network Management (per OSEK-NM)                           |     |

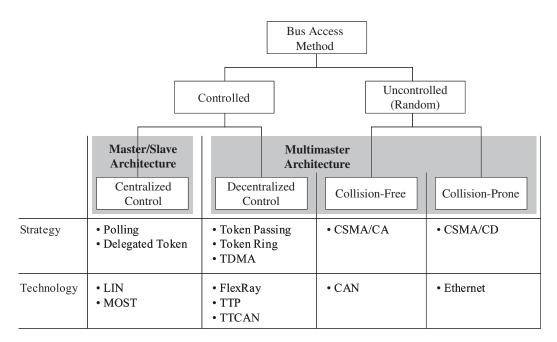

|     | 2.5.6   | Strategies for Bus Arbitration                                     |     |

|     |         | 2.5.6.1 Bus Access Strategies—Centralized or Decentralized         |     |

|     |         | Implementation                                                     | 98  |

|     |         | 2.5.6.2 Bus Access Strategies—Controlled or Random                 | 98  |

|     |         | 2.5.6.3 Bus Access Strategies-Event-Driven and Time-Controlled     |     |

| 2.6 | System  | Reliability, Safety, Monitoring, and Diagnostics                   |     |

|     | 2.6.1   | Basic Terms                                                        |     |

|     | 2.6.2   | System Reliability and Availability                                |     |

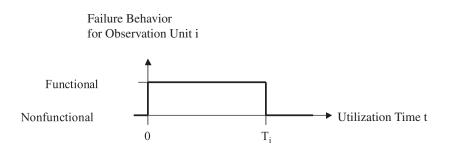

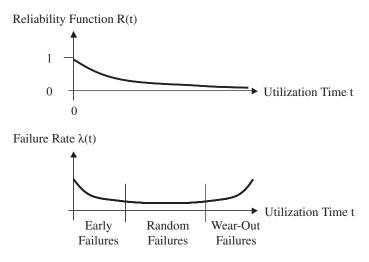

|     |         | 2.6.2.1 Definition of Reliability Function R(t) and                |     |

|     |         | Failure Rate $\lambda(t)$                                          | 102 |

|     |         | 2.6.2.2 Definition of Mean Time to Failure (MTTF)                  |     |

|     |         | × /                                                                |     |

|     |       | 2.6.2.3 Definition of Mean Time to Repair (MTTR)                                    | 105   |

|-----|-------|-------------------------------------------------------------------------------------|-------|

|     |       | 2.6.2.4 Definition of Mean Availability                                             | 106   |

|     | 2.6.3 | System Safety                                                                       | 107   |

|     |       | 2.6.3.1 Definition of Terms in Safety Technology                                    | 107   |

|     |       | 2.6.3.2 Determining Risk                                                            | 108   |

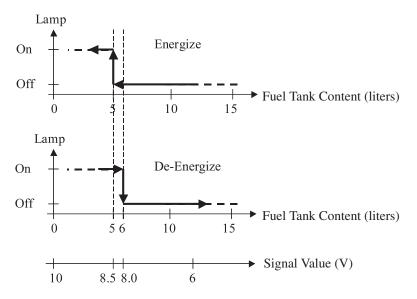

|     | 2.6.4 | System Monitoring and Diagnostics                                                   | 110   |

|     |       | 2.6.4.1 Monitoring                                                                  | 110   |

|     |       | 2.6.4.2 Fault Recognition and Fault Diagnostics                                     | 111   |

|     |       | 2.6.4.3 Error Detection and Correction                                              | 112   |

|     |       | 2.6.4.4 Safety Logic                                                                |       |

|     |       | 2.6.4.5 Functional Software Safety                                                  |       |

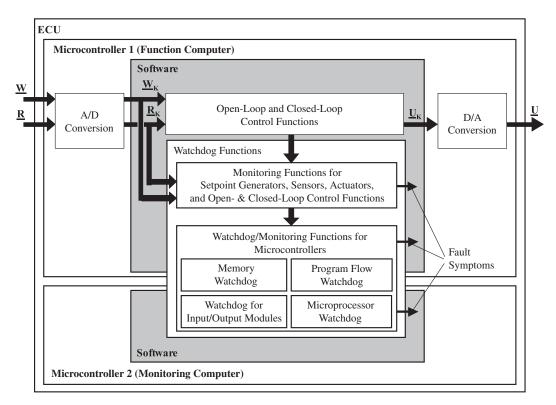

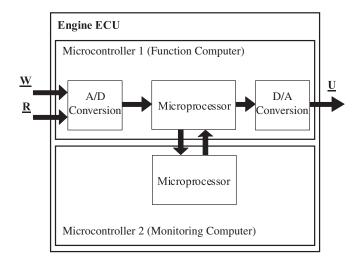

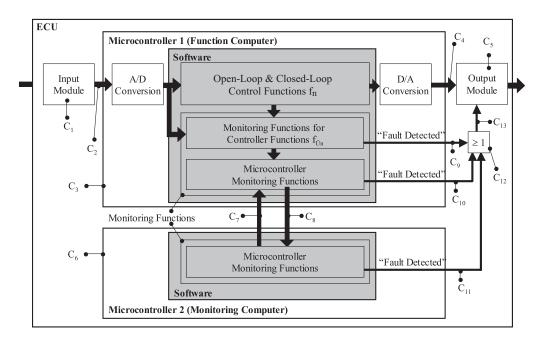

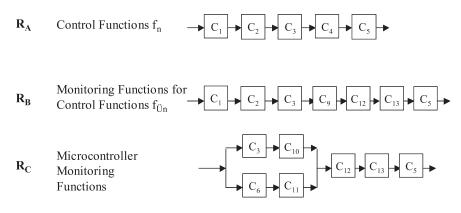

|     | 2.6.5 | Organization of a Monitoring System for Electronic Control Units                    | 115   |

|     |       | 2.6.5.1 Microcontroller Monitoring Functions                                        | 116   |

|     |       | 2.6.5.2 Monitoring Setpoint Generators, Sensors, Actuators, and                     |       |

|     |       | Control Functions                                                                   | 117   |

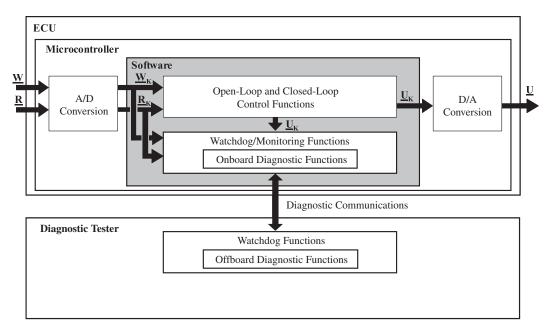

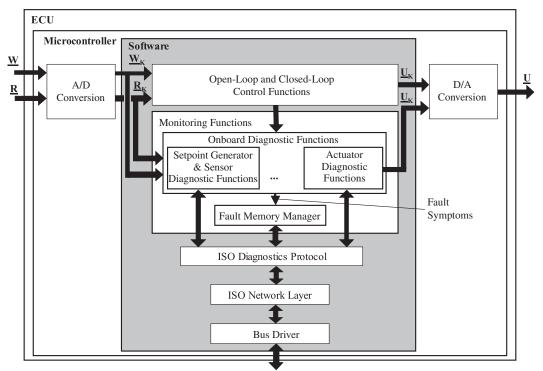

|     | 2.6.6 | Organization of a Diagnostic System for Electronic Control Units                    | 118   |

|     |       | 2.6.6.1 Offboard Diagnostic Functions                                               |       |

|     |       | 2.6.6.2 Onboard Diagnostic Functions                                                |       |

|     |       | 2.6.6.3 Diagnostics for Setpoint Generators and Sensors                             | 120   |

|     |       | 2.6.6.4 Diagnostics for Actuators                                                   |       |

|     |       | 2.6.6.5 Fault Memory Manager                                                        |       |

|     |       | 2.6.6.6 Offboard Diagnostic Communications                                          |       |

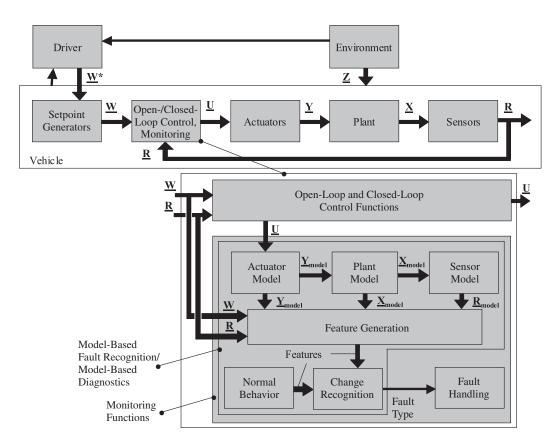

|     |       | 2.6.6.7 Model-Based Fault Recognition                                               | 122   |

| 2.7 | Summa | ary                                                                                 | 123   |

|     | _     |                                                                                     |       |

|     |       | cesses for Electronic Systems and Software Engineering                              |       |

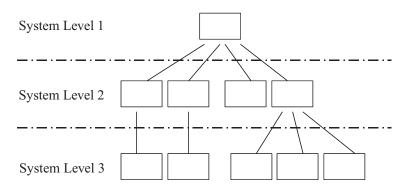

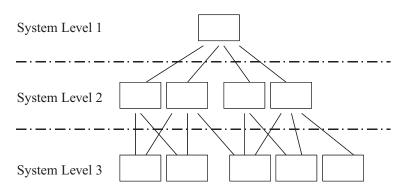

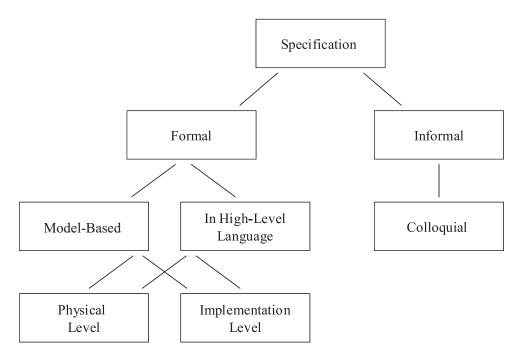

| 3.1 |       | Definitions of System Theory                                                        |       |

| 3.2 |       | s Models and Standards                                                              |       |

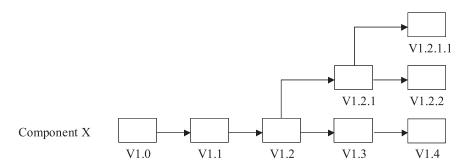

| 3.3 |       | uration Management                                                                  |       |

|     | 3.3.1 | Product and Life Cycle                                                              |       |

|     | 3.3.2 | Variants and Scalability                                                            |       |

|     | 3.3.3 | Versions and Configurations                                                         |       |

| 3.4 |       | Management                                                                          |       |

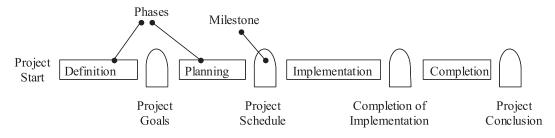

|     | 3.4.1 | Project Planning                                                                    |       |

|     |       | 3.4.1.1 Quality Planning                                                            |       |

|     |       | 3.4.1.2 Cost Planning                                                               |       |

|     |       | 3.4.1.3 Project Scheduling                                                          |       |

|     |       | 3.4.1.4 Development Roles and Responsibilities                                      |       |

|     | 3.4.2 | Project Tracking and Risk Management                                                |       |

| 3.5 |       | ntractor Management                                                                 |       |

|     | 3.5.1 | System and Component Responsibilities                                               |       |

|     | 3.5.2 | Interfaces for Specification and Integration                                        |       |

|     | 3.5.3 | Defining the Cross-Corporation Development Process                                  |       |

| 3.6 | -     | ements Management                                                                   |       |

|     | 3.6.1 | Mining, Recording, and Interpreting User Requirements<br>Tracking User Requirements |       |

|     | 3.6.2 |                                                                                     | 1 5 0 |

3.

|    | 3.7  | Quality      | y Assurance                                                       | 154 |  |  |

|----|------|--------------|-------------------------------------------------------------------|-----|--|--|

|    |      | 3.7.1        | Integration and Testing Procedures                                | 154 |  |  |

|    |      | 3.7.2        | Software Quality Assurance Methods                                | 155 |  |  |

| 4. | Core | Process      | s for Electronic Systems and Software Engineering                 | 157 |  |  |

|    | 4.1  |              | ements and Prerequisites                                          |     |  |  |

|    |      | 4.1.1        | Shared System and Component Responsibilities                      |     |  |  |

|    |      | 4.1.2        | Coordination of Systems Engineering and Software Engineering      |     |  |  |

|    |      | 4.1.3        |                                                                   |     |  |  |

|    | 4.2  |              | Definitions and Notations                                         |     |  |  |

|    |      | 4.2.1        |                                                                   |     |  |  |

|    |      | 4.2.2        |                                                                   |     |  |  |

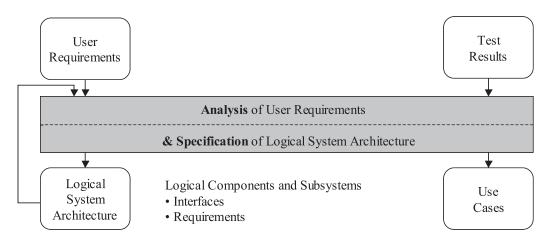

|    | 4.3  | Analys       | sis of User Requirements and Specification of Logical System      |     |  |  |

|    | 4 4  |              | ecture                                                            | 164 |  |  |

|    | 4.4  |              | sis of Logical System Architecture and Specification of Technical | 167 |  |  |

|    |      | 4.4.1        | Analysis and Specification of Open-Loop/Closed-Loop Control       | 10/ |  |  |

|    |      | 4.4.1        | Systems                                                           | 171 |  |  |

|    |      | 4.4.2        | Analysis and Specification of Real-Time Systems                   |     |  |  |

|    |      | 4.4.2        | Analysis and Specification of Distributed and Networked Systems   |     |  |  |

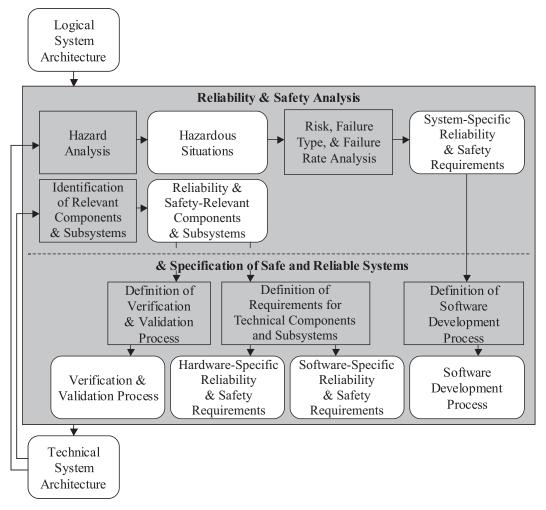

|    |      | 4.4.3        | Analysis and Specification of Reliable and Safe Systems           |     |  |  |

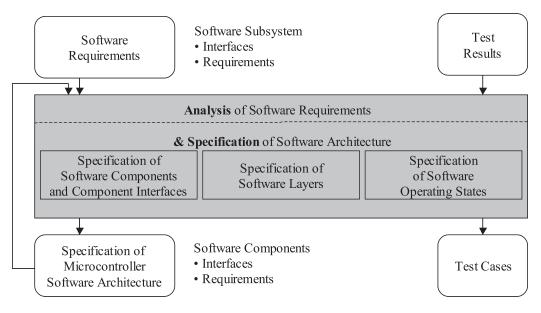

|    | 4.5  |              | sis of Software Requirements and Specification of Software        | 173 |  |  |

|    | 4.3  | Architecture |                                                                   |     |  |  |

|    |      | 4.5.1        | Specification of Software Components and Associated Interfaces    |     |  |  |

|    |      | 4.3.1        | 4.5.1.1 Specification of Onboard Interfaces                       |     |  |  |

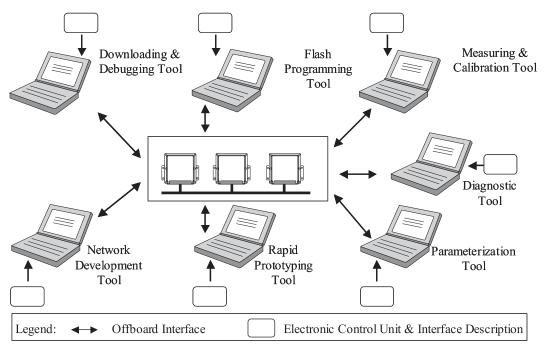

|    |      |              | 4.5.1.2 Specification of Offboard Interfaces                      |     |  |  |

|    |      | 4.5.2        | Specification of Software Layers                                  |     |  |  |

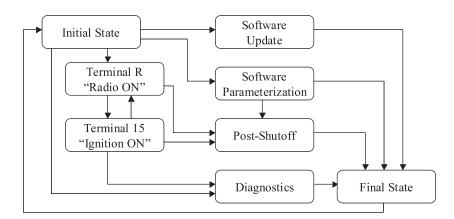

|    |      | 4.5.3        | Specification of Operating States                                 |     |  |  |

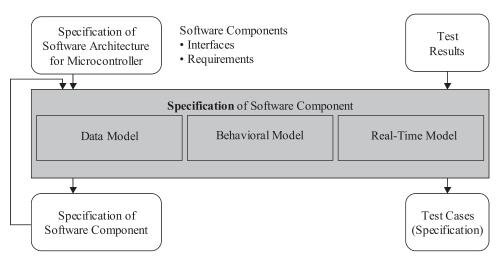

|    | 4.6  |              | ication of Software Components                                    |     |  |  |

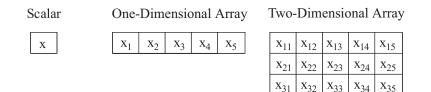

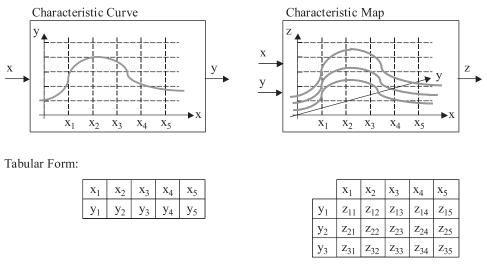

|    | 1.0  | 4.6.1        | Specification of Data Model                                       |     |  |  |

|    |      | 4.6.2        | Specification of Behavioral Model                                 |     |  |  |

|    |      | 1.0.2        | 4.6.2.1 Specification of Data Flow                                |     |  |  |

|    |      |              | 4.6.2.2 Specification of Control Flow                             |     |  |  |

|    |      | 4.6.3        | Specification of Real-Time Model                                  |     |  |  |

|    |      | 1.0.5        | 4.6.3.1 State-Dependent Reactive Execution Model                  |     |  |  |

|    |      |              | 4.6.3.2 State-Independent Reactive Execution Model                |     |  |  |

|    | 4.7  | Design       | and Implementation of Software Components                         |     |  |  |

|    |      | 4.7.1        | Consideration of Requested Nonfunctional Product Properties       |     |  |  |

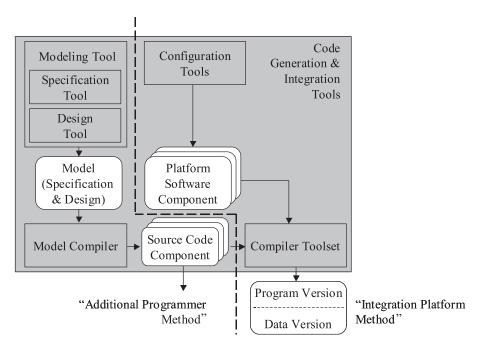

|    |      |              | 4.7.1.1 Differentiation Between Program Version and Data Version. |     |  |  |

|    |      |              | 4.7.1.2 Limitation of Hardware Resources                          |     |  |  |

|    |      | 4.7.2        | Design and Implementation of Data Model                           |     |  |  |

|    |      | 4.7.3        | Design and Implementation of Behavioral Model                     |     |  |  |

|    |      | 4.7.4        | Design and Implementation of Bendvious Model                      |     |  |  |

|    | 4.8  |              | are Component Testing                                             |     |  |  |

|    | 4.9  |              | ation of Software Components                                      |     |  |  |

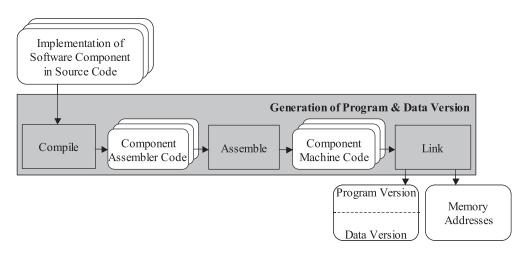

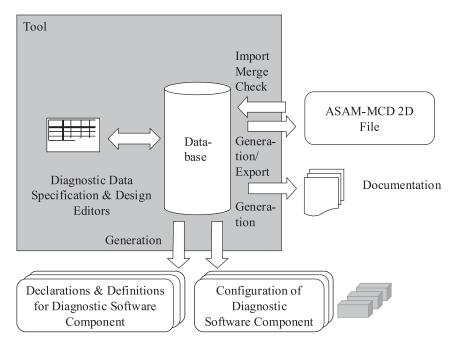

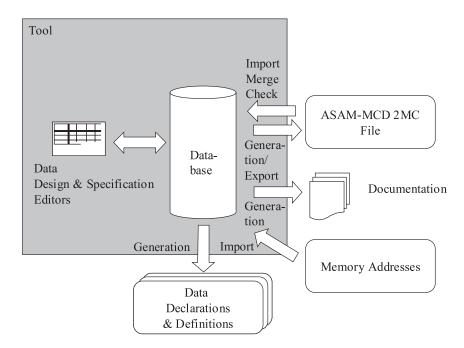

|    |      | 4.9.1        | Generating Program Version and Data Version                       |     |  |  |

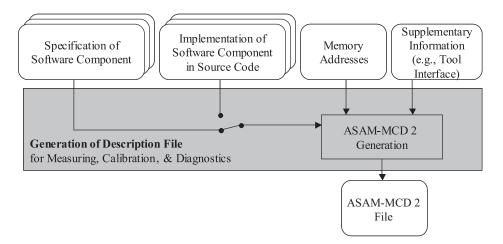

|    |                  | 4.9.2          | Generating Description Files                                                       | 197 |

|----|------------------|----------------|------------------------------------------------------------------------------------|-----|

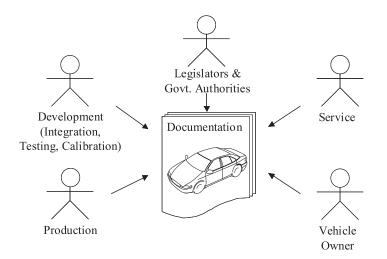

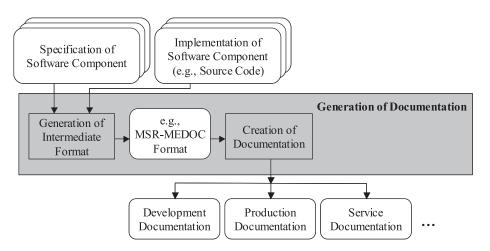

|    |                  | 4.9.3          | Generating Documentation                                                           |     |

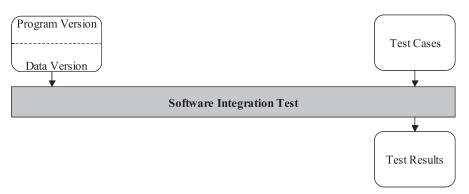

|    | 4.10             | Softwa         | re Integration Testing                                                             | 199 |

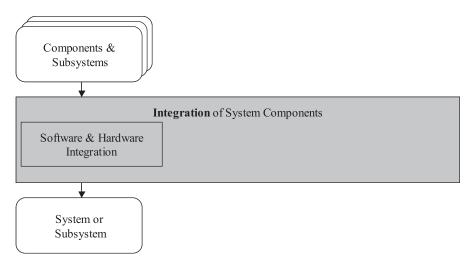

|    | 4.11             | Integra        | tion of System Components                                                          | 200 |

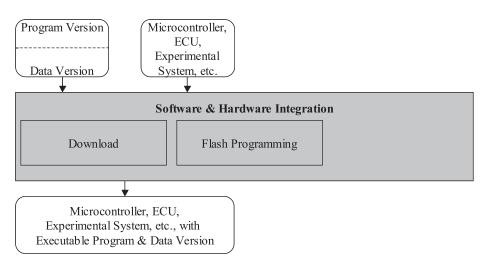

|    |                  | 4.11.1         | Integration of Software and Hardware                                               | 201 |

|    |                  |                | 4.11.1.1 Download                                                                  | 201 |

|    |                  |                | 4.11.1.2 Flash Programming                                                         |     |

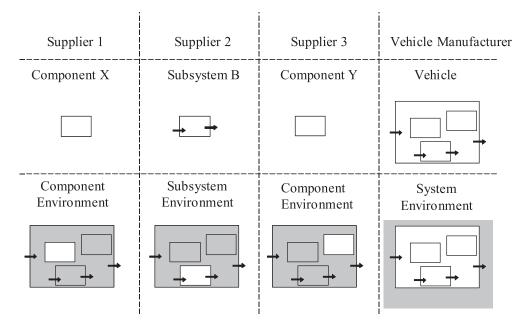

|    |                  | 4.11.2         | Integration of ECUs, Setpoint Generators, Sensors, and Actuators                   | 202 |

|    | 4.12             | System         | Integration Test                                                                   | 203 |

|    | 4.13             |                | tion                                                                               |     |

|    | 4.14             | System         | and Acceptance Test                                                                | 208 |

| _  | N <i>T</i> - 41- |                |                                                                                    | 211 |

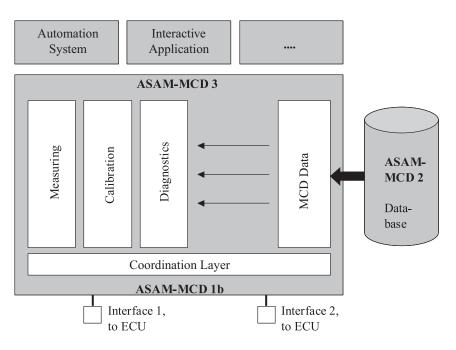

| 5. | 5.1              |                | I Tools for Development<br>rd Interface Between Electronic Control Units and Tools |     |

|    | 5.1<br>5.2       |                |                                                                                    | 212 |

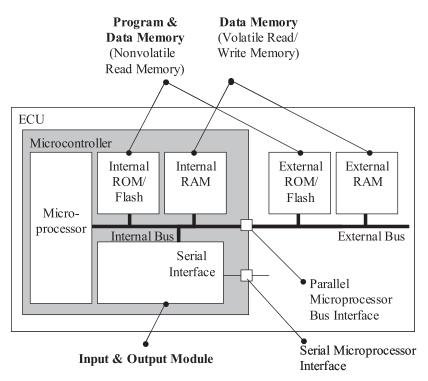

|    | 5.2              | -              | is of Logical System Architecture and Specification of Technical                   | 212 |

|    |                  | 5              | Architecture                                                                       | 213 |

|    |                  | 5.2.1          | Analysis and Specification of Open-Loop and Closed-Loop                            | 214 |

|    |                  | 5.2.2          | Control Systems                                                                    |     |

|    |                  | 3.2.2          | Analysis and Specification of Real-Time Systems                                    |     |

|    |                  |                | 5.2.2.1 Schedulability Analysis                                                    |     |

|    |                  |                | 5.2.2.2 Verifying Schedulability by Means of Measurements                          | 224 |

|    |                  |                | 5.2.2.3 Monitoring and Handling Deadline Violations in the<br>Operating System     | 224 |

|    |                  | 5.2.3          | Analysis and Specification of Distributed and Networked Systems                    |     |

|    |                  | 5.2.5<br>5.2.4 | Analysis and Specification of Reliable and Safe Systems                            |     |

|    |                  | 3.2.4          | 5.2.4.1 Failure Rate Analysis and Calculation of Reliability                       | 229 |

|    |                  |                | Function                                                                           | 220 |

|    |                  |                | 5.2.4.2 System Safety and Reliability Analysis                                     |     |

|    | 5.3              | Specifi        | cation of Software Functions and Validation of Specification                       |     |

|    | 5.5              | 5.3.1          | Specification of Software Architecture and Software Components                     |     |

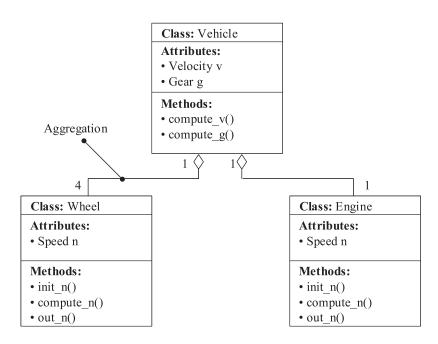

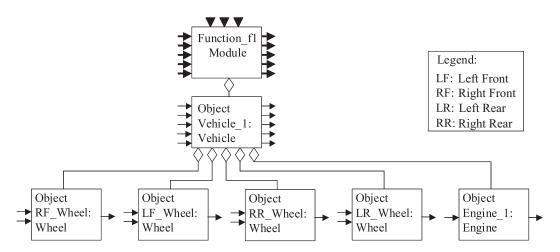

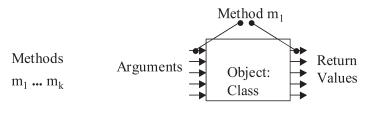

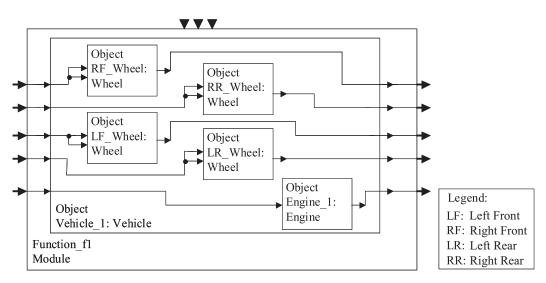

|    |                  | 5.5.1          | 5.3.1.1 Object-Based Software Architecture Modeling                                |     |

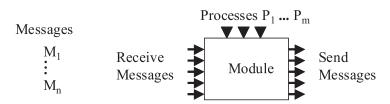

|    |                  |                | 5.3.1.2 Module-Based Specification of Interfaces to Real-Time                      | 240 |

|    |                  |                | Operating System                                                                   | 242 |

|    |                  |                | 5.3.1.3 Class-Based Specification of Reusable Software                             | 272 |

|    |                  |                | Components                                                                         | 243 |

|    |                  | 5.3.2          | Specification of Data Model                                                        |     |

|    |                  | 5.3.3          | Specification of Behavioral Model Using Block Diagrams                             |     |

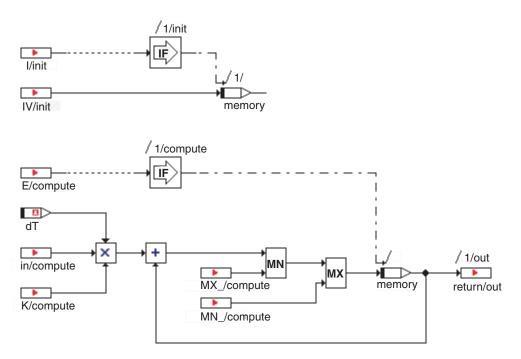

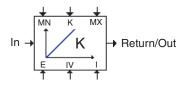

|    |                  | 5.5.5          | 5.3.3.1 Specification of Arithmetical Functions                                    |     |

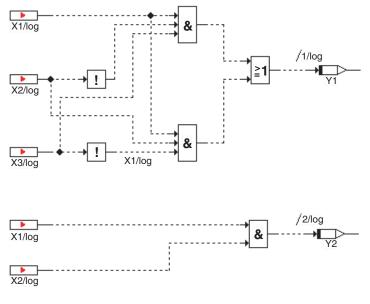

|    |                  |                | 5.3.3.2 Specification of Boolean Functions                                         |     |

|    |                  | 5.3.4          | Specification of Behavioral Model Using Decision Tables                            |     |

|    |                  | 5.3.5          | Specification of Behavioral Model Using State Machines                             |     |

|    |                  | 2.2.10         | 5.3.5.1 Specifying Flat State Machines                                             |     |

|    |                  |                | 5.3.5.2 Specifying Transitions with Branching Instructions                         |     |

|    |                  |                | 5.3.5.3 Specifying Hierarchy State Machines                                        |     |

|    |                  | 5.3.6          | Specification of Behavioral Model Using High-Level Languages                       |     |

|    |                  | 5.3.7          | Specification of Real-Time Model                                                   |     |

|    |                  |                |                                                                                    |     |

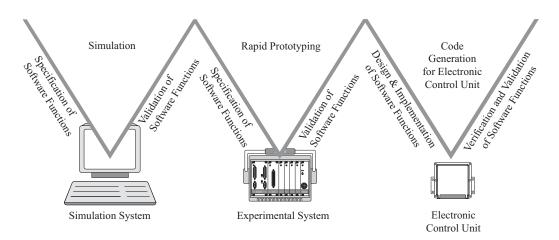

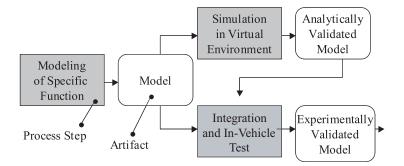

|     | 5.3.8   | Validating | g the Specification Through Simulation and Rapid         |     |

|-----|---------|------------|----------------------------------------------------------|-----|

|     |         | Prototypi  | ng                                                       | 258 |

|     |         | 5.3.8.1    | Simulation                                               | 258 |

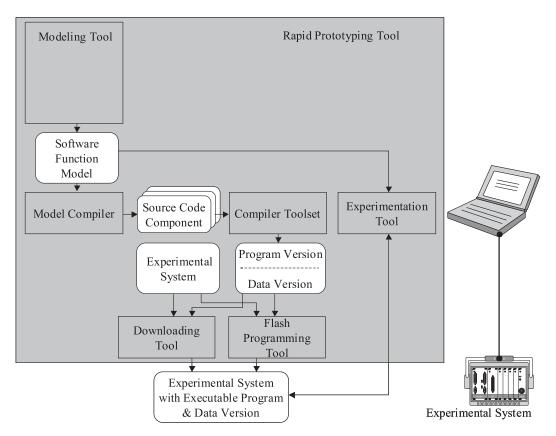

|     |         | 5.3.8.2    | Rapid Prototyping                                        | 259 |

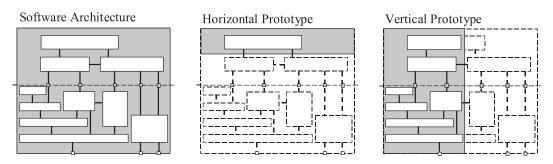

|     |         | 5.3.8.3    | Horizontal and Vertical Prototypes                       | 261 |

|     |         | 5.3.8.4    | Target System Identical Prototypes                       |     |

|     |         | 5.3.8.5    | Throw-Away and Evolutionary Prototypes                   |     |

|     |         | 5.3.8.6    | Reference Prototype for ECU Verification                 |     |

| 5.4 | Design  |            | mentation of Software Functions                          |     |

| 0.1 | 5.4.1   |            | ation of Requested Nonfunctional Product Properties      |     |

|     | 0.111   | 5.4.1.1    | Runtime Optimization Through Consideration of Varying    | 207 |

|     |         | 0          | Access Times to Different Memory Segments                | 269 |

|     |         | 5.4.1.2    | Runtime Optimization Through Distribution of Software    | 20) |

|     |         | 5.1.1.2    | Function to Several Tasks                                | 270 |

|     |         | 5.4.1.3    | Resource Optimization Through Division into Online       | 270 |

|     |         | 5.7.1.5    | and Offline Calculations                                 | 271 |

|     |         | 5.4.1.4    | Resource Optimization Through Division into Onboard      | 271 |

|     |         | J.T.1.T    | and Offboard Calculations                                | 272 |

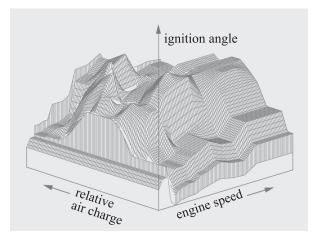

|     |         | 5/15       | Resource Optimization for Characteristic Curves and Maps |     |

|     | 5.4.2   |            | ad Implementation of Algorithms for Fixed-Point and      | 215 |

|     | 3.4.2   | -          | Point Arithmetic                                         | 777 |

|     |         | 5.4.2.1    | Representation of Numbers in Digital Processors          |     |

|     |         | 5.4.2.1    | Rounding Errors in Integer Division                      |     |

|     |         | 5.4.2.2    | Overflow and Underflow in Addition, Subtraction, and     | 201 |

|     |         | 3.4.2.3    | Multiplication                                           | 202 |

|     |         | 5.4.2.4    | Shift Operations                                         |     |

|     |         |            | <b>▲</b>                                                 |     |

|     |         | 5.4.2.5    | Handling Overflows and Underflows                        | 284 |

|     |         | 5.4.2.6    | Error Propagation with Algorithms in Fixed-Point         | 200 |

|     |         | 5 4 2 7    | Arithmetic                                               |     |

|     |         | 5.4.2.7    | Physical Interrelation and Fixed-Point Arithmetic        |     |

|     |         | 5.4.2.8    | Physical Model Level and Implementation Level            |     |

|     |         | 5.4.2.9    | Notes on Implementation in Fixed-Point Arithmetic        |     |

|     |         | 5.4.2.10   | Notes on Implementation in Floating-Point Arithmetic     |     |

|     |         | 5.4.2.11   | Modeling and Implementation Guidelines                   |     |

|     | 5.4.3   | -          | nd Implementation of Software Architecture               |     |

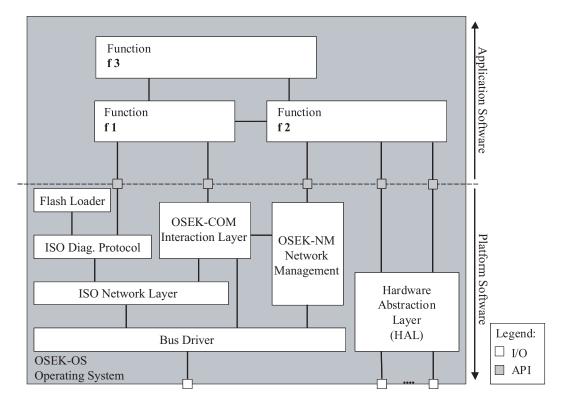

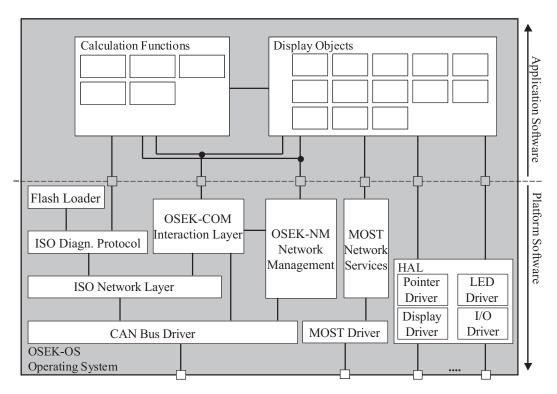

|     |         | 5.4.3.1    | Platform and Application Software                        |     |

|     |         | 5.4.3.2    | Standardization of Platform Software Components          |     |

|     |         | 5.4.3.3    | Configuration of Standardized Software Components        |     |

|     | 5.4.4   |            | nd Implementation of Data Model                          |     |

|     |         | 5.4.4.1    | Definition of Memory Segment                             |     |

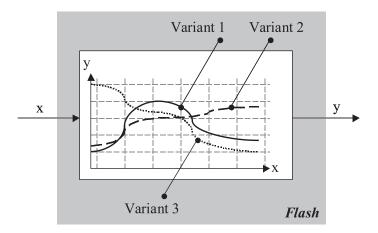

|     |         | 5.4.4.2    | Setting Data Variants via Flash Programming              |     |

|     |         | 5.4.4.3    | Setting Data Variants via Configuration Parameters       |     |

|     |         | 5.4.4.4    | Generation of Data Structures and Description Files      |     |

|     | 5.4.5   |            | nd Implementation of Behavioral Model                    |     |

| 5.5 | Integra |            | esting of Software Functions                             |     |

|     | 5.5.1   | Software   | -in-the-Loop Simulations                                 | 309 |

|     | 5.5.2   | Laboratory Vehicles and Test Benches                             |

|-----|---------|------------------------------------------------------------------|

|     |         | 5.5.2.1 Test Environment for Standalone ECUs                     |

|     |         | 5.5.2.2 Test Environment for ECUs, Setpoint Generators, Sensors, |

|     |         | and Actuators                                                    |

|     |         | 5.5.2.3 Test Environment for ECU Network                         |

|     |         | 5.5.2.4 Test Bench                                               |

|     | 5.5.3   | Experimental, Prototype, and Production Vehicles                 |

|     | 5.5.4   | Design and Automation of Experiments                             |

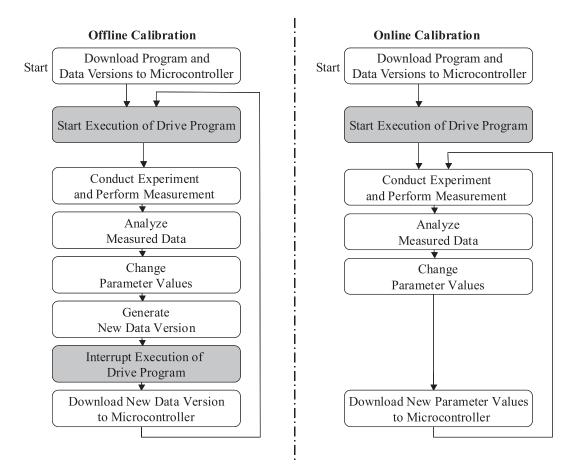

| 5.6 | Calibra | tion of Software Functions                                       |

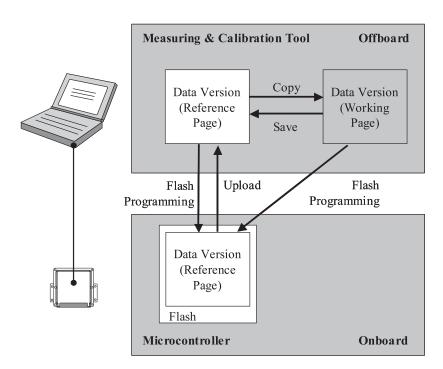

|     | 5.6.1   | Offline and Online Calibration Procedures                        |

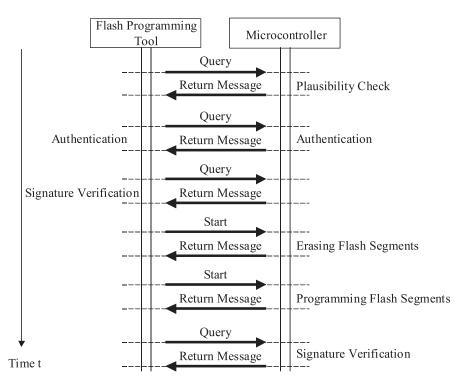

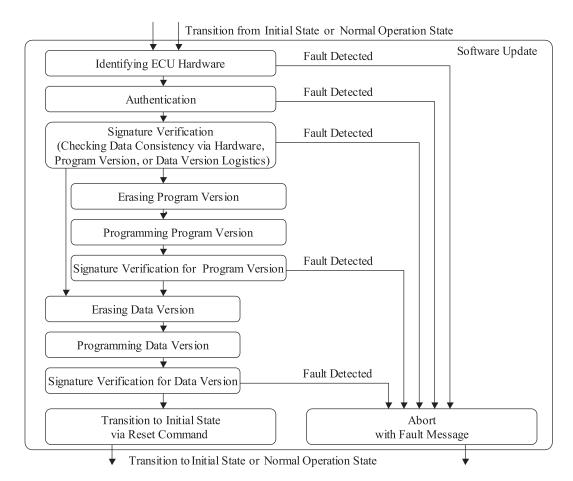

|     | 5.6.2   | Software Update Through Flash Programming                        |

|     | 5.6.3   | Synchronous Measuring of Microcontroller and Instrumentation     |

|     |         | Signals                                                          |

|     | 5.6.4   | Downloading and Evaluating Onboard Diagnostic Data               |

|     | 5.6.5   | Offline Calibration of Parameters                                |

|     | 5.6.6   | Online Calibration of Parameters                                 |

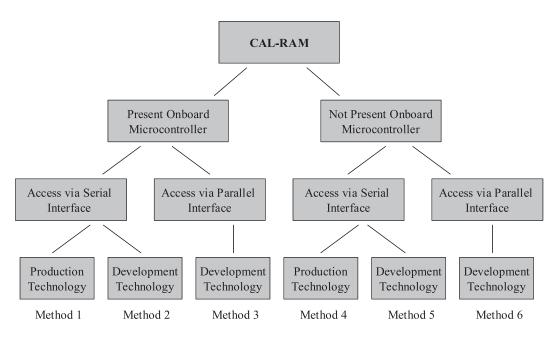

|     | 5.6.7   | Classification of Offboard Interfaces for Online Calibration     |

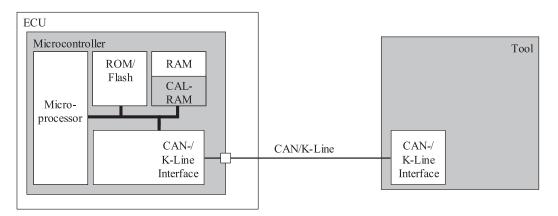

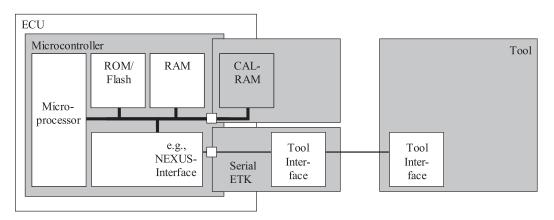

|     |         | 5.6.7.1 Serial Preproduction Interface with Internal CAL-RAM     |

|     |         | (Method 1)                                                       |

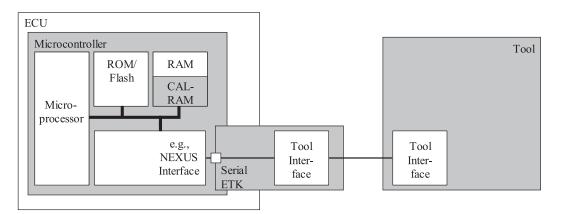

|     |         | 5.6.7.2 Serial Development Interface with Internal CAL-RAM       |

|     |         | (Method 2)                                                       |

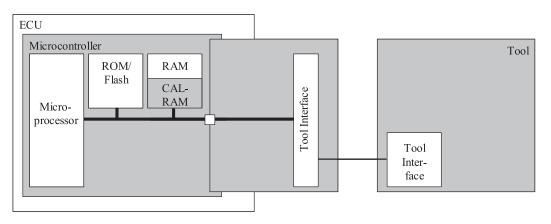

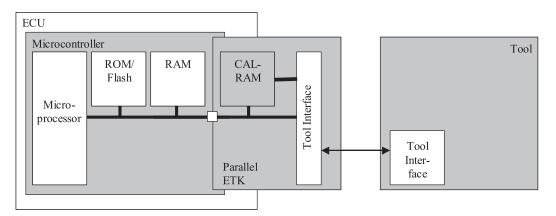

|     |         | 5.6.7.3 Parallel Development Interface with Internal CAL-RAM     |

|     |         | (Method 3)                                                       |

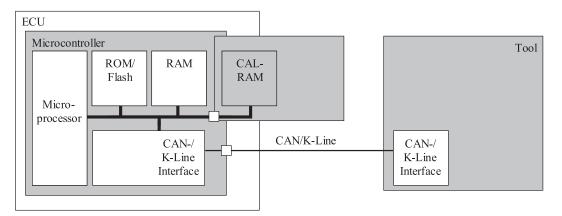

|     |         | 5.6.7.4 Serial Preproduction Interface with Additional CAL-RAM   |

|     |         | (Method 4)                                                       |

|     |         | 5.6.7.5 Serial Development Interface withAdditional CAL-RAM      |

|     |         | (Method 5)                                                       |

|     |         | 5.6.7.6 Parallel Development Interface withAdditional CAL-RAM    |

|     |         | (Method 6)                                                       |

|     |         | 5.6.7.7 Communications Protocols for Calibration Tools and       |

|     |         | Microcontrollers                                                 |

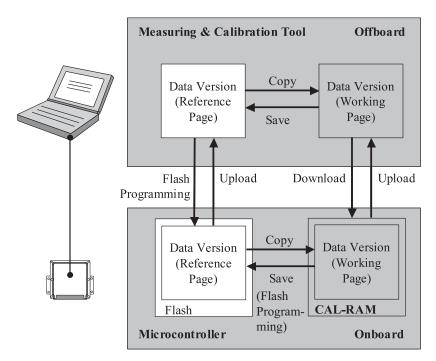

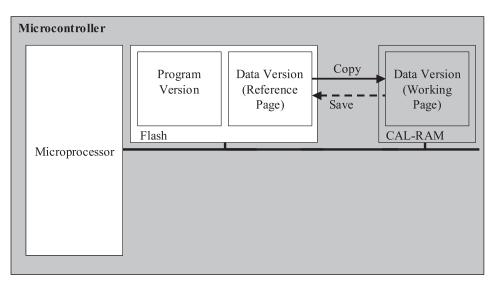

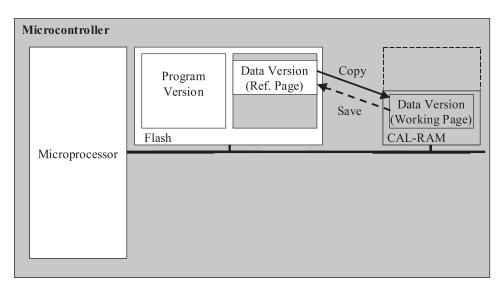

|     | 5.6.8   | CAL-RAM Management                                               |

|     |         | 5.6.8.1 CAL-RAM Management with Sufficient Memory Resources 333  |

|     |         | 5.6.8.2 CAL-RAM Management with Limited Memory Resources 334     |

|     | 5.6.9   | Parameter and Data Version Management                            |

|     |         | 5.6.9.1 Binary Program and Data Version File Calibration         |

|     |         | 5.6.9.2 Model or Source Code Calibration and Optimization        |

|     | 5.6.10  | Design and Automation of Experiments 337                         |

|     |         |                                                                  |

| Met |         | I Tools for Production and Service                               |

| 6.1 |         | rd Diagnostics                                                   |

| 6.2 |         | eterization of Software Functions                                |

| 6.3 |         | re Update Through Flash Programming                              |

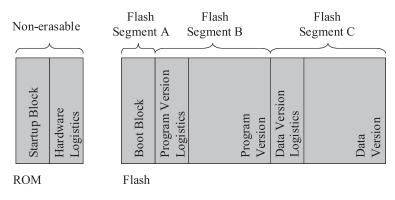

|     | 6.3.1   | Erasing and Programming Flash Memory                             |

|     | 6.3.2   | Flash Programming Through the Offboard Diagnostic Interface      |

|     | 6.3.3   | Security Requirements                                            |

6.

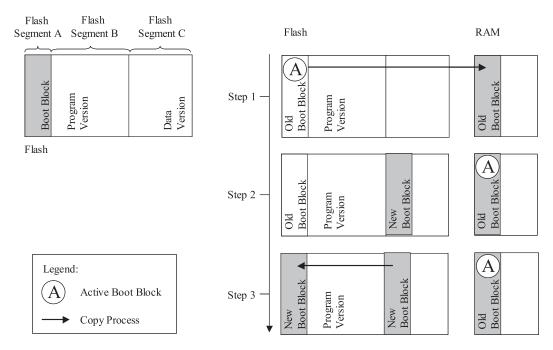

|      |         |         | Availability Requirements<br>Boot Block Shifting and Flash Programming |     |

|------|---------|---------|------------------------------------------------------------------------|-----|

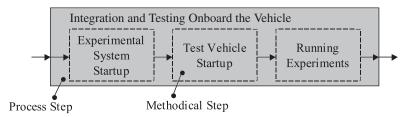

|      | 6.4     |         | and Testing of Electronic Systems                                      |     |

| 7.   | Sum     | mary an | d Outlook                                                              | 351 |

| Re   | ferenc  | es      |                                                                        | 355 |

| Illı | ıstrati | on Cred | its                                                                    | 363 |

| Lis  | t of A  | cronyms | ·                                                                      | 365 |

| Inc  | lex     |         |                                                                        | 369 |

| Ab   | out th  | e Autho | rs                                                                     | 385 |

## CHAPTER ONE

## INTRODUCTION AND OVERVIEW

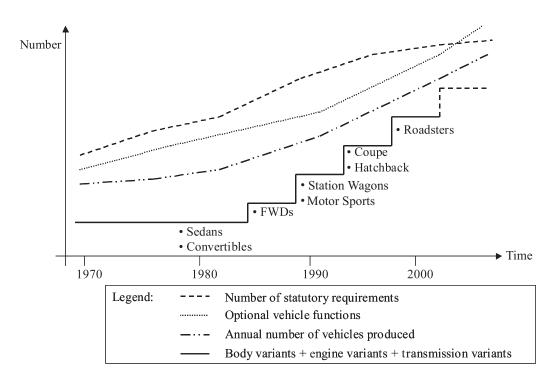

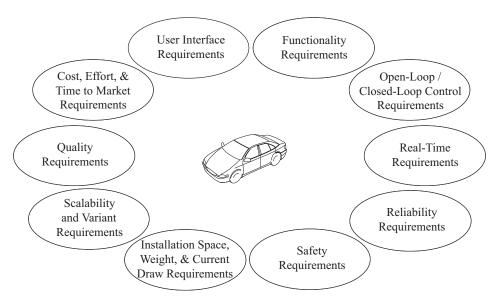

The fulfillment of increasing customer demands and stringent legal requirements with regard to reducing fuel consumption and harmful emissions, and increasing driving safety and driver/ passenger comfort, is inextricably linked to the advancement of electronics in modern vehicles.

As a result, the automobile has become today's most technically complex consumer article. However, note that the requirements for automotive electronics differ substantially from those for other areas of consumer goods electronics. The most prominent requirements for automotive electronics are as follows:

- Deployment under frequently harsh environmental conditions (e.g., temperature range, humidity, vibration) or stringent demands on electromagnetic compatibility (EMC)

- Stringent reliability and availability requirements

- Stringent operational safety demands

- Comparatively long product life cycles

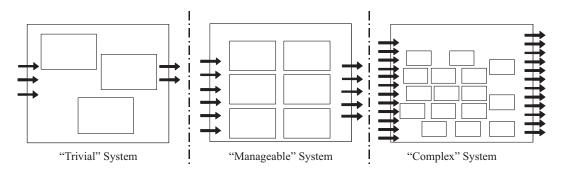

Although the requirements for electronic components for vehicles are stringent, developers still face high pressure for low cost, shortened development cycles, and a great number of model variants. Regardless, these requirements must be fulfilled for products that can be manufactured in high volume.

To bring a development project in onboard automotive electronics to a successful conclusion, project leaders must manage the increasing complexity of their products while maintaining a consistent quality and managing both risk and cost.

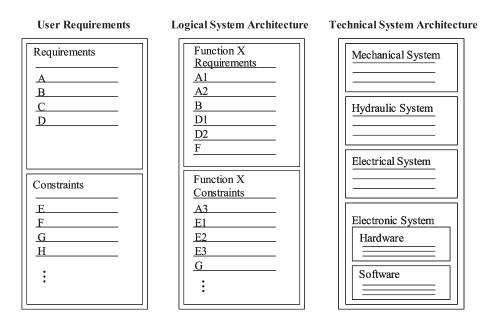

A basic understanding of the requirements for and trends in vehicle engineering is essential for anyone who wants to develop suitable methods for development, production, and service of electronic systems for vehicles and who wants to support these by praxis-oriented standards and tools. This introductory chapter provides an analysis of the current state of the art, as background for a description of future perspectives and the associated challenges.

Following an overview of automotive electronic systems and their functions, this chapter introduces the methods used to develop electronic systems and software for automotive applications. The chapter concludes with an introduction to model-based engineering methods.

The remaining chapters of this book feature detailed discussions of essential system basics (Chapter 2), processes (Chapters 3 and 4), and methods and tools (Chapter 5) for the development

of software for automotive electronics, as well as the production and service of software for automotive electronics (Chapter 6). Throughout the book, special emphasis is given to vehicle subsystems such as powertrain, chassis, and vehicle body. The book introduces the field of multimedia systems but does not cover it in detail. Chapter 7 provides a summary review of the topics discussed throughout the book. It also outlines the future prospects and challenges for the development of automotive electronics.

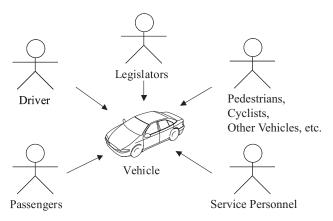

### 1.1 The Driver-Vehicle-Environment System

The objective of any development project is the completion of a new, or the improvement of an existing, function for the vehicle. In the context of this book, the term *function* denotes all of the functional features of the vehicle. These functions ultimately provide a value or benefit to the user (i.e., the operator of the vehicle) that the latter is able to experience directly or that he or she can perceive only indirectly.

The question whether the technical implementation of a given functional feature involves a mechanical, hydraulic, electrical, or electronic system onboard the vehicle is of minor importance from the user's point of view.

However, from the point of view of the engineer who is implementing the functions, the use of electronic components combined with mechanical, electrical, or hydraulic systems provides numerous benefits, especially with regard to attainable reliability, weight, required installation space, and cost. For all of these reasons, electronics has become the key technology in the implementation of many innovations in automotive construction. In fact, nearly all functions of the vehicle today are electronically controlled or monitored.

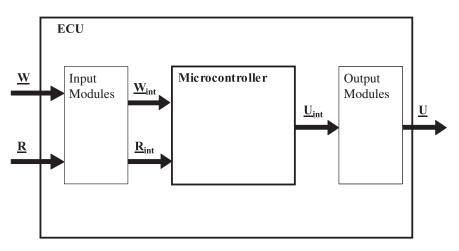

## 1.1.1 Design and Method of Operation of Vehicle Electronic Systems

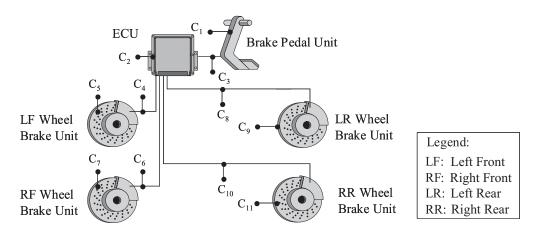

The following provides a closer look at the design and method of operation of electronic systems in the vehicle, using an electrohydraulic braking system as an example.

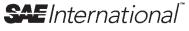

#### Example: Configuration of Sensotronic brake control [1]

Figure 1-1 shows the system configuration of the Bosch Sensotronic brake control (SBC) [1]. The electrohydraulic braking system combines the functions of brake booster, antilock braking system (ABS), and electronic stability program (ESP).

The driver's mechanical actuation of the brake pedal is registered in the brake pedal unit and is transmitted electrically to the so-called *electronic control unit* (ECU). The ECU uses this setpoint and additional signals from various sensors, such as the steering angle signal or wheel rotational speed signal, to calculate output variables that again are electronically transmitted to the hydraulic modulator. There they are converted by means of brake-pressure modulation to variables for the wheel brakes. The wheel brakes influence the vehicle drivability, the so-called *controlled system* or *plant*. Thus, the wheel brakes are referred to as actuators.

Fig. 1-1. Diagram of the Bosch Sensotronic brake control (SBC). (Ref. [1])

Because the ECU communicates with other ECUs onboard the vehicle via a data bus (e.g., the CAN bus [2]), functions that go beyond those mentioned so far and that involve more than a single ECU also can be implemented. One example of this kind of function is the *traction control system* (TCS), which represents a mediating function between engine management and the braking system.

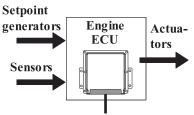

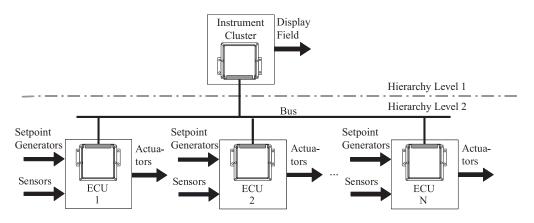

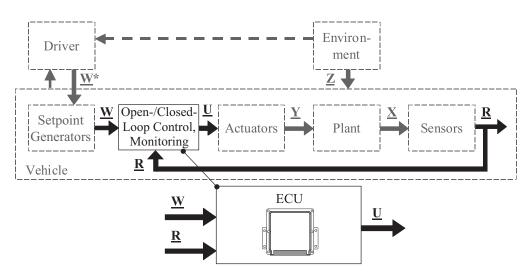

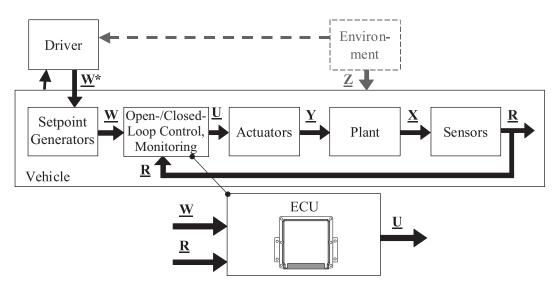

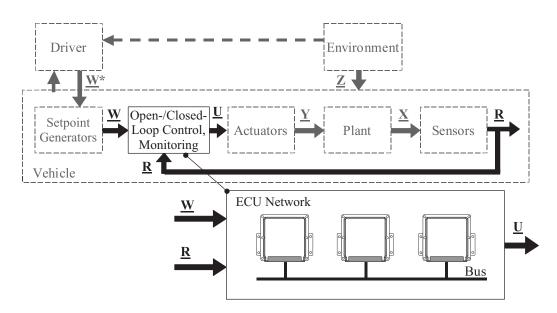

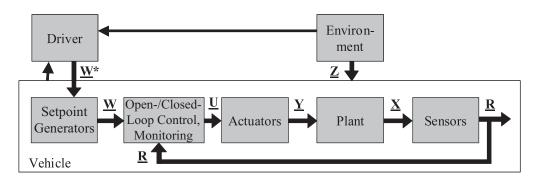

The system configuration of the electrohydraulic braking system exemplifies the typical configuration of all electronic control (open-loop/closed-loop) and monitoring systems of the vehicle. Generally, the following components are involved in such a system: setpoint generators, sensors, actuators, ECUs, and the controlled system, the so-called *plant*. The networked interconnection of the involved ECUs facilitates the exchange of data.

The driver and the environment—considered components of the higher-level driver–vehicle– environment system—are able to influence the way the vehicle behaves.

Seen alone, an ECU merely represents a means to an end, because it is—as an isolated component—of no apparent value to the vehicle user. Only a complete system comprising ECUs, setpoint generators, sensors, and actuators will influence and monitor the plant (i.e., respond to the actions or requests of the user). However, in many situations, and especially when, as is frequently the case, so-called *embedded systems* are at work, the electronic implementation of functions is not even visible to the vehicle user.

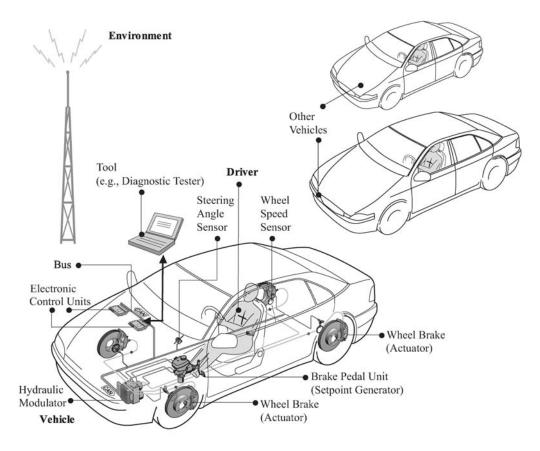

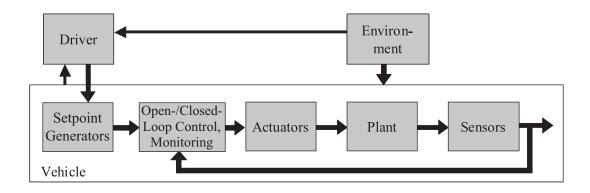

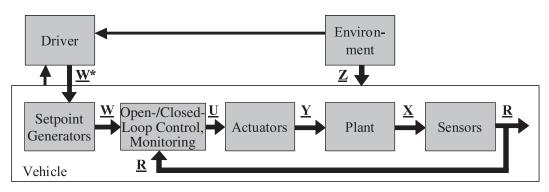

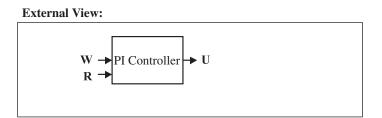

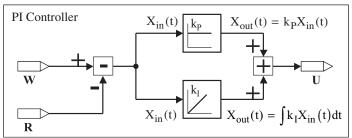

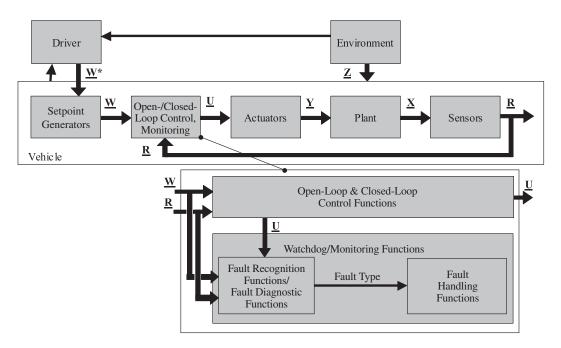

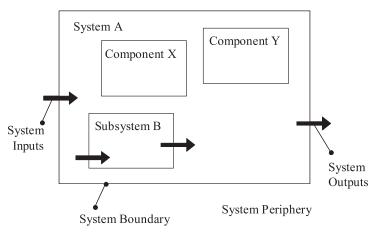

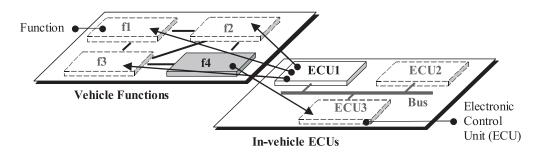

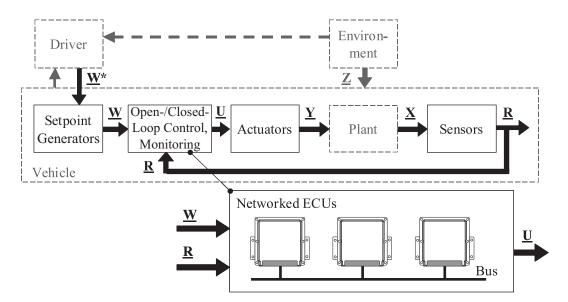

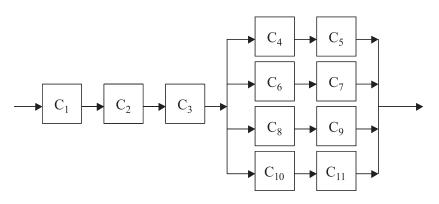

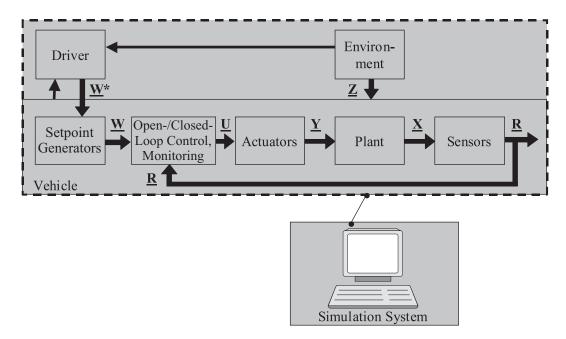

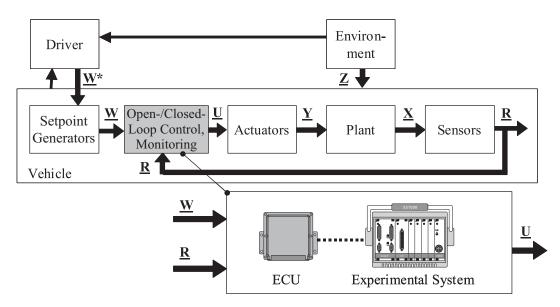

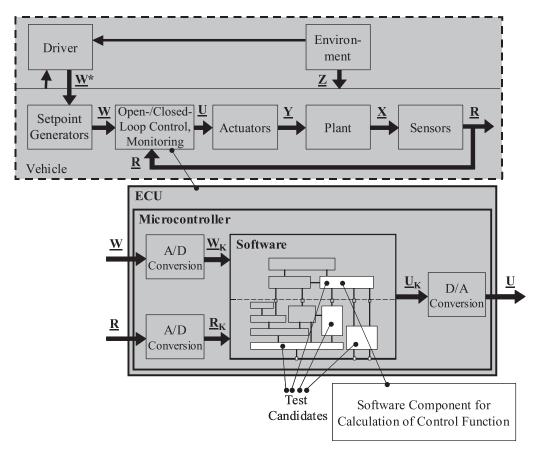

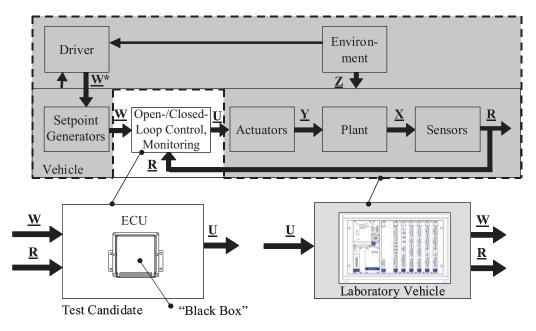

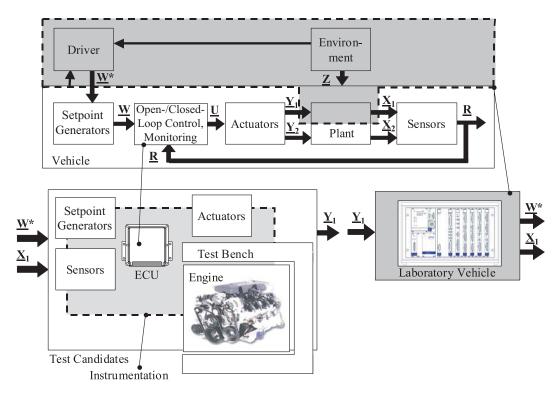

As shown in Fig. 1-2, control and monitoring systems onboard the vehicle can be represented as a structured block diagram. Components are shown as blocks, with arrows depicting the signal flow between the blocks. For an introduction to the fundamentals and terminology of control and monitoring technology, see Sections 2.1 and 2.6 in Chapter 2.

Fig. 1-2. Block diagram of control and monitoring systems.

As shown in Fig. 1-2, signal flow may exist among a number of the components (i.e., the driver, vehicle, and environment). In this figure, the driver serves as a placeholder for all users of a particular vehicle function (i.e., for driver and passengers).

The environment also encompasses other vehicles, as well as electronic systems located in proximity to the vehicle. These include tools, such as diagnostic test equipment in the service shop, that are connected to the electronic systems onboard the vehicle (Fig. 1-1).

New technologies aiding the exchange of information between driver and vehicle, driver and environment, and vehicle and environment facilitate a plethora of innovative functions—an example would be networking beyond the physical periphery of the vehicle by means of wireless communication systems. The idea of networking beyond the physical periphery of the vehicle enables a new class of systems (e.g., driver assistance systems). During the past few years, the area of multimedia systems in particular has seen the introduction of many functions that became feasible only through vehicle–environment networking. One example is the dynamic navigation

feature, which considers environment-specific information (e.g., traffic gridlock reports) in the process of route computation.

Another area that has benefitted from many recent innovations is the area of interfaces (i.e., the interaction—through so-called *user interfaces*—between the driver and/or passengers and the vehicle). For example, operating and display systems today may be based on voice control concepts.

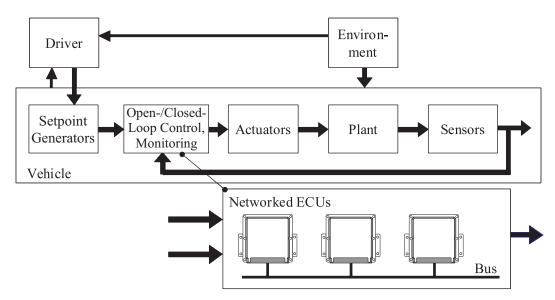

In light of the foregoing, discussions of the term *networking* throughout this book will not be limited to only the electronic functions of the vehicle, but will include electronic functions or systems that interact with the driver and vehicle from outside the physical boundaries of that vehicle. Therefore, it is helpful at this point of the discussion to introduce and define the terms *onboard* and *offboard*, and *online* and *offline*.

### 1.1.2 Electronic Systems of the Vehicle and the Environment

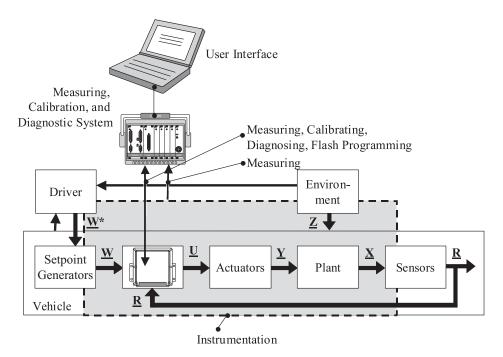

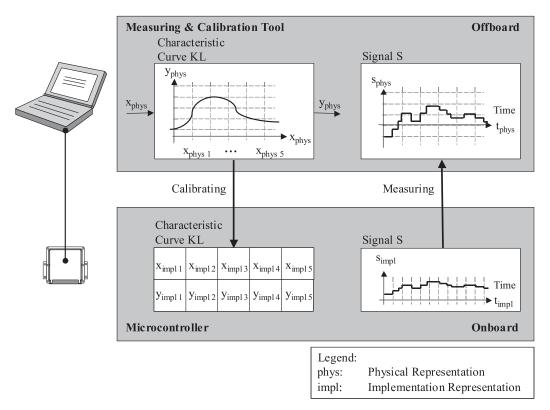

Throughout subsequent chapters, communications among electronic systems in the vehicle is termed *onboard communications*. By contrast, communications linking the onboard systems of the vehicle and systems in the environment is called *offboard communications*. A similar differentiation between *onboard* and *offboard interfaces* is made when referring to the interfaces of the electronic systems in the vehicle. Figure 1-3 provides an overview.

Fig. 1-3. Electronic systems of the vehicle and the environment.

With regard to the functions performed by the electronic systems of the vehicle and those handled by systems in the environment, a differentiation is made between *onboard functions* and *offboard functions*, respectively. The division of functions into subfunctions and the distributed implementation of subfunctions by means of both onboard and offboard systems are also conceivable.

Another differentiation characteristic is the point in time at which a given function is executed by an offboard system, relative to the point in time at which a function is executed by an onboard system. In this case, a differentiation is made between the synchronized execution (also referred to as *online* execution) and the unsynchronized execution of functions (*offline* execution).

For several years, the onboard/offboard and online/offline differentiation criteria have been used in the context of diagnostic systems for vehicle functions, giving rise to the distinction between onboard and offboard diagnostics, a term that by now surely is familiar to many readers. Design methods and tools dedicated to the development of automotive electronic systems are designated in a similar fashion.

### 1.2 Overview of Vehicle Electronic Systems

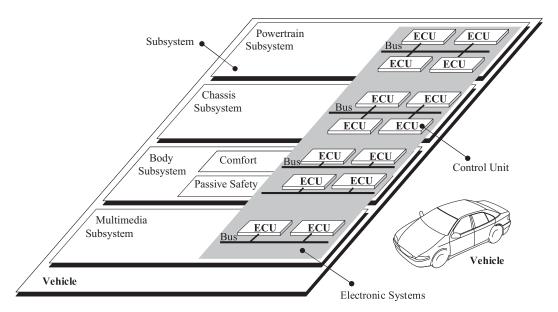

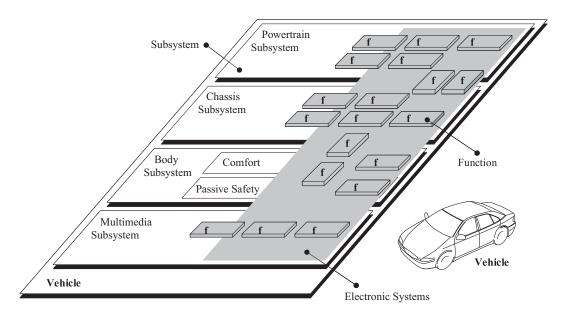

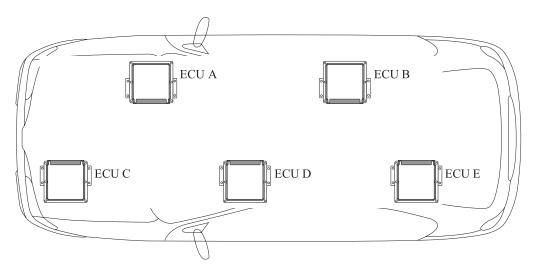

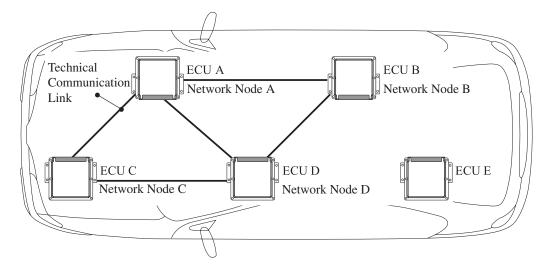

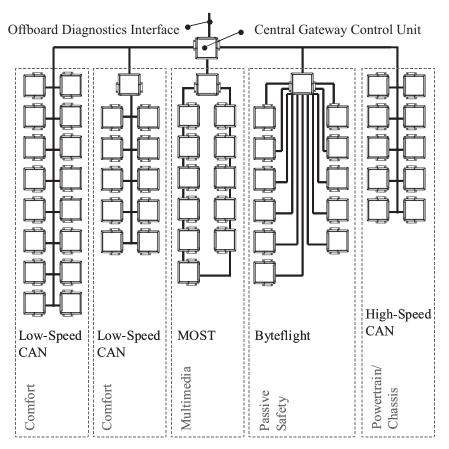

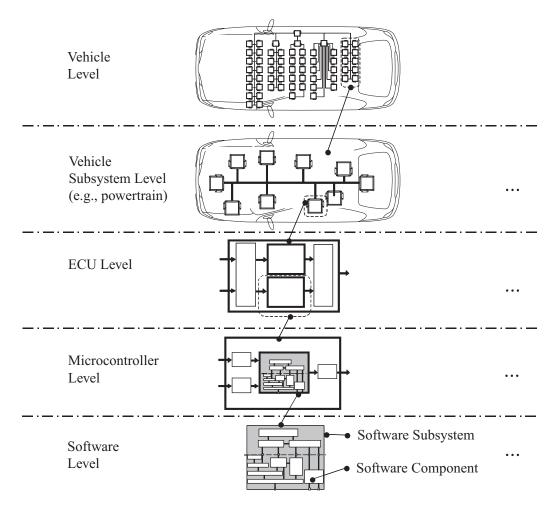

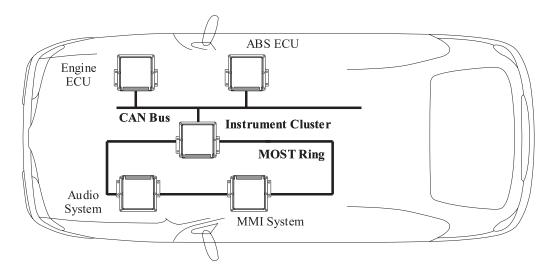

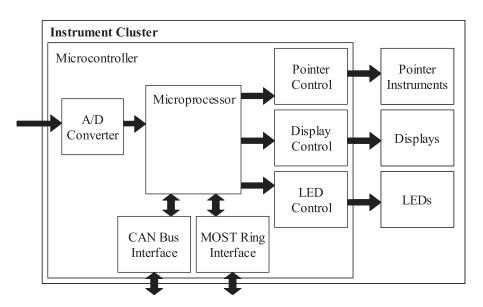

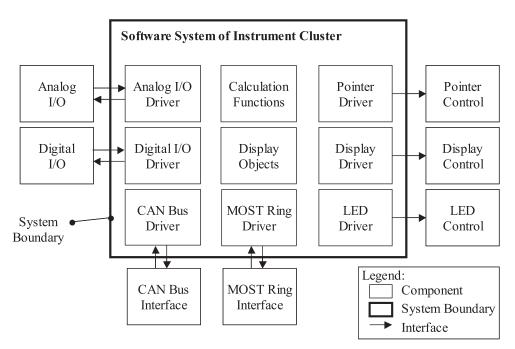

By way of introduction, the various electronic systems onboard a vehicle are presented in an overview. Vehicles typically contain more than one ECU for the controlling and monitoring of various subsystems. In the early days of the deployment of electronics in the vehicle, the operation of these ECUs was largely autonomous. With no interaction among ECUs, it was relatively easy to assign functions associated with a specific vehicle subsystem, such as power-train, chassis, body, and multimedia, to the ECU responsible for controlling and monitoring that subsystem (Fig. 1-4).

Fig. 1-4. Assignment of ECUs to vehicle subsystems.

Thus, the classic systems of engine management and transmission control are assigned to the powertrain, and the antilock braking system (ABS) to the chassis subsystem, whereas the heating and air conditioning system, central locking system, and seat and mirror adjustment are part of the comfort and convenience subsystem belonging to the body subsystem. Contributing to increased vehicle occupant safety in the event of an accident, the airbag and restraint systems belong to the passive safety system, whereas radio and telephone are part of the multimedia system.

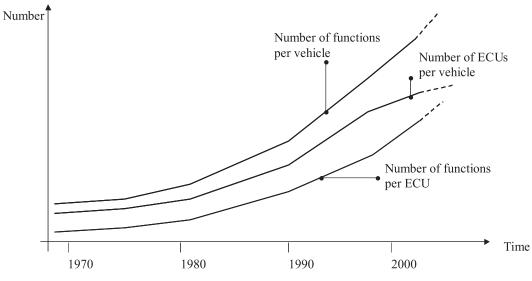

The continuing quantum leaps in hardware technology and performance facilitate the implementation of many increasingly powerful vehicle functions by means of software. These functions are referred to as *software functions*.

The introduction of powerful bus systems, such as the CAN (Controller Area Network) bus [2] in the early1990s, initiated the second phase of ECU technology. Networking of electronic systems was now possible and with it, the implementation of new higher-level software functions, as well as the associated cost savings. For example, multiple systems could use signals from individual sensors without the need for costly wiring connections.

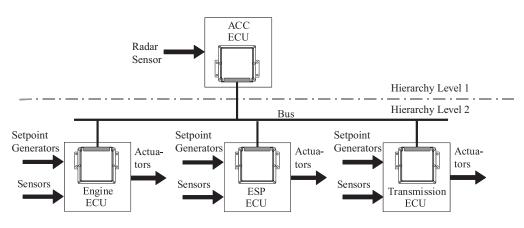

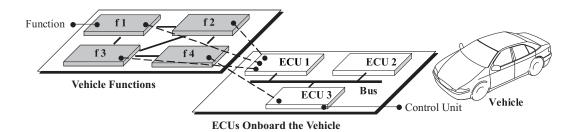

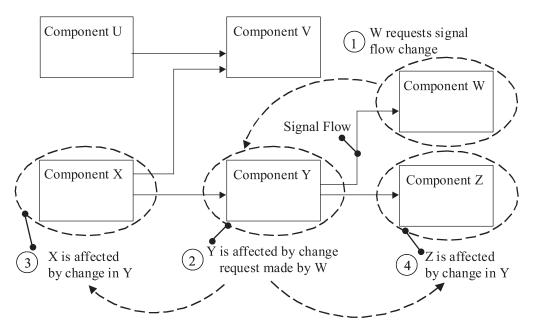

Whenever higher-level software functions influence any functions of a single subsystem, this implementation approach is also known as an integrated powertrain, integrated chassis, integrated body, or integrated safety management. In distributed and networked systems, however, it is often no longer possible to assign software functions to a single ECU. As a result, software functions are divided into subfunctions for implementation in several ECUs.

Whenever higher-level software functions influence functions of several subsystems, they can no longer be assigned to one specific subsystem. As discussed in the context of the introductory example, the traction control system (TCS) comprises a set of functions that affects both powertrain and chassis. Many other driver assistance systems, such as distance-sensing adaptive cruise control, also belong to this category. Functions working across subsystem boundaries exist in the areas of comfort systems and passive safety systems. One example of such a set of functions is the vehicle access system that includes the locking and theft deterrent systems. These examples underscore the fact that transitions among subsystems are at best fluid if seen from a functional standpoint.

Multiple access to and use of *sensor* signals by various ECUs can be handled in most instances without difficulty. As soon as various ECUs (or better, several software functions) *compete* for access to the same *actuators*, however, the developer is presented with serious challenges, one of which is that of finding a suitable method of specification. Another challenge is the definition of interfaces for accurate data and request exchange among the various functions and systems, so that, for example, commands sent to various actuators can be clearly coordinated. For a more detailed discussion of this and related topics, please consult CARTRONIC [3].

Following an overview of the electronic systems assisting the powertrain, chassis, and body groups, this section also describes multimedia systems. Although these systems are not given wide exposure within the context of this book, an overview is nevertheless helpful for the purposes of identifying multimedia boundaries *vis-à-vis* those of the other application areas. Finally, several examples of functions are discussed, whose implementation is possible only after the electronic systems are communicating within a network.

In this section, systems are classified according to typical features, such as the following:

- User interfaces and setpoint generators

- Sensors and actuators

- Software functions

- Installation space

- Model variants and scalability

Current and foreseeable trends are considered and referenced in the discussion.

In many cases, the technical implementation of functions must consider a number of legal regulations. For example, any development in powertrain—in particular, the development of software functions for engine ECUs—often is driven by guidelines and laws concerning fuel economy and exhaust emissions. By contrast, the development of chassis and body group functions is driven mostly by safety and comfort requirements.

This section limits the discussion to an overview of automotive electronic systems and their functions. Individual aspects of electronic function and system development will be examined more closely in subsequent chapters, using appropriate examples. For a comprehensive treatment of these topics, please refer to the extensive specialist literature (e.g., [4]).

## 1.2.1 Electronic Systems of the Powertrain

The powertrain of a vehicle encompasses the following units and components:

- Drive group (i.e., internal combustion engine, electric motor, hybrid drive, or fuel cell)

- Clutch and manual transmission, or automatic transmission

- Transfer case, front- and/or rear-axle drive

- Driveshafts and propshafts

- Engine auxiliary systems, such as the starter and alternator

The electronic systems of the driveshaft include the following:

- Engine ECUs

- Transmission ECUs

A variety of control and monitoring functions for engine, transmission, and auxiliary units use as input variables driver requests and a number of sensor signals and thus are able to control the actuators in the powertrain.

#### 1.2.1.1 User Interfaces and Setpoint Generators

The electronic powertrain control functions have a relatively small number of user interfaces. Other than by starting the engine and shutting it off, the driver can directly transmit his or her requests only by changing the position of the accelerator pedal. A manual transmission provides two additional user interfaces, the clutch pedal and the shift lever; an automatic transmission merely offers one, the drive selector. Additional user interfaces may be required to meet special needs, such as mode selector switches for automatic transmissions.

#### 1.2.1.2 Sensors and Actuators

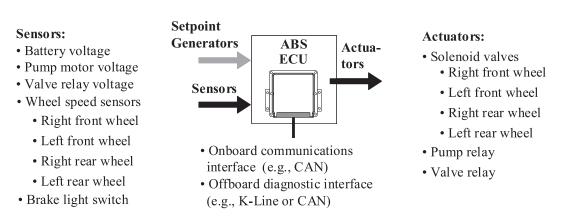

A relatively large contingent of sensors is required, for example, to capture attitude and position, rotational speeds, pressures, temperatures, lambda values, or engine-knock intensity. This is complemented by a similarly large number of actuators handling ignition, injection, throttle valve, clutches, or valves. This results in a large number of ECU interfaces. Figure 1-5 shows the interfaces of an engine ECU. Onboard communications are handled primarily via the CAN bus [2]. For dedicated offboard communication with the diagnostic tester, the K-Line [5] is being progressively replaced by the CAN bus [2].

#### Setpoint generators:

- Accelerator pedal position

- Transmission stage

#### Sensors:

- Throttle valve position

- Air mass

- Battery voltage

- Intake air temperature

- Engine temperature

- Knock intensity

- Lambda oxygen sensors

- Crankshaft speed and top dead center

- Camshaft lobe control

- Vehicle speed

- :

- Onboard communications interface (e.g., CAN)

- Offboard diagnostic interface (e.g., K-Line or CAN)

- Spark plugs

- Electronic throttle control

- Fuel injectors

- Fuel supply pump relay

- Lambda sensor heater

- Fuel tank ventilation

- Variable-tract intake manifold

- Secondary-air valve

- Exhaust-gas recirculation valve

- :

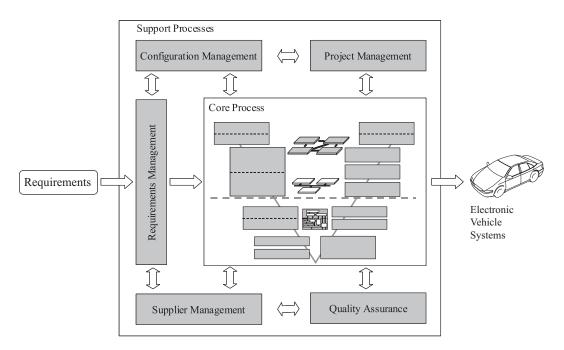

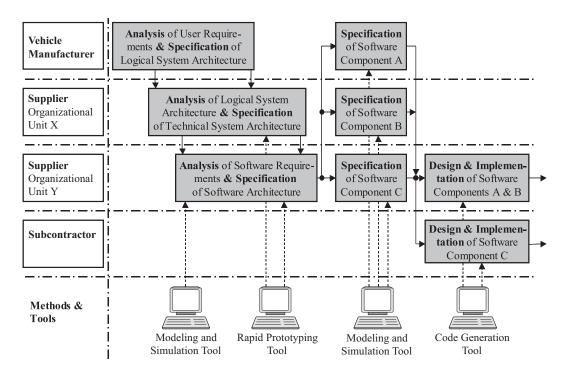

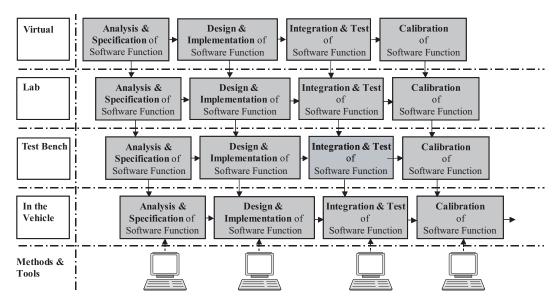

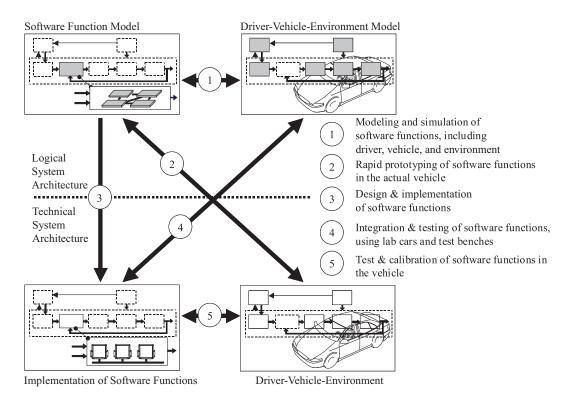

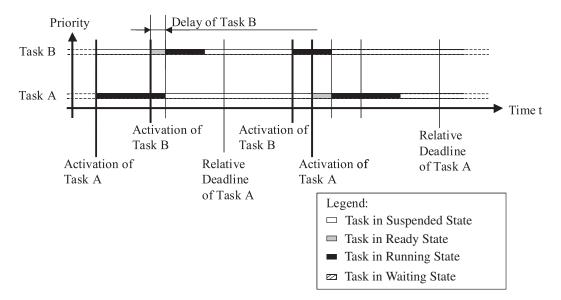

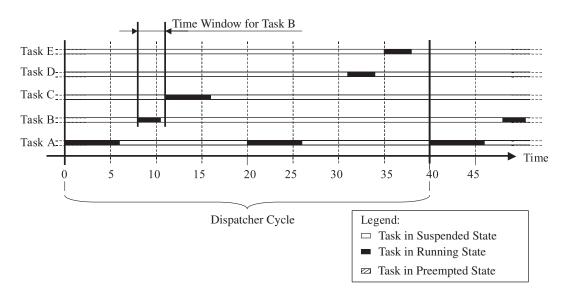

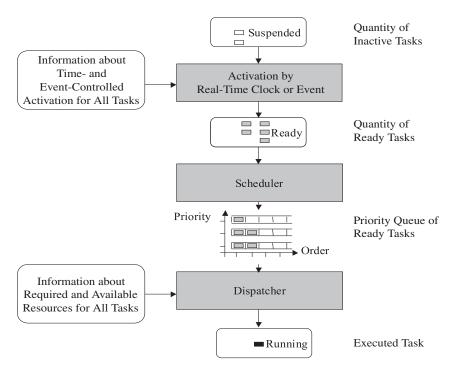

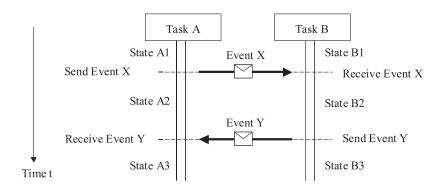

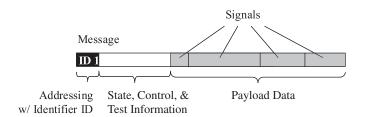

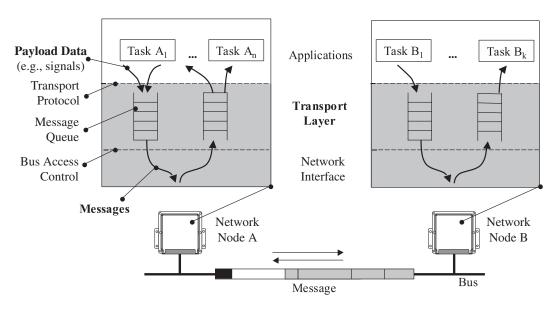

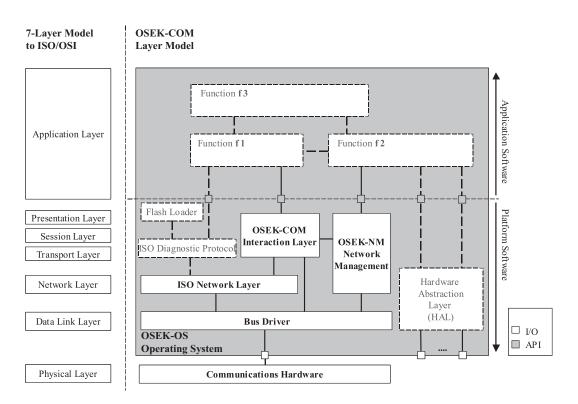

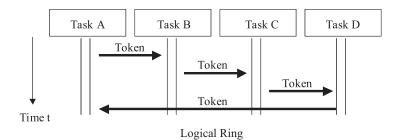

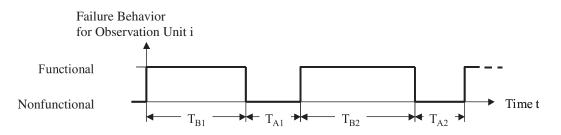

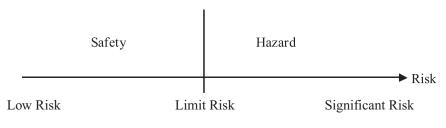

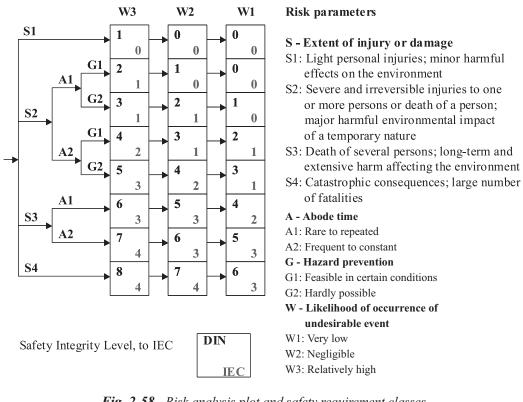

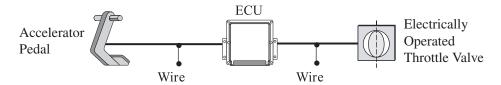

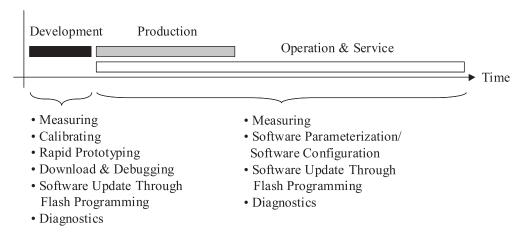

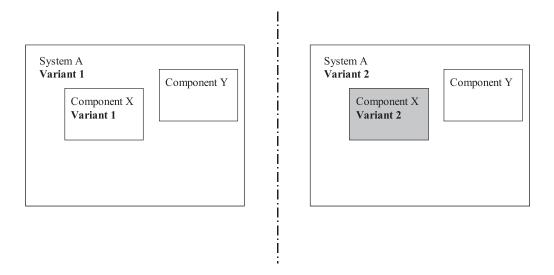

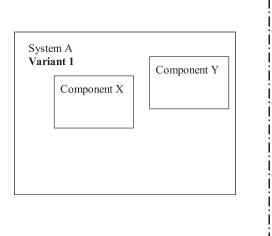

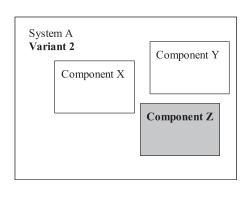

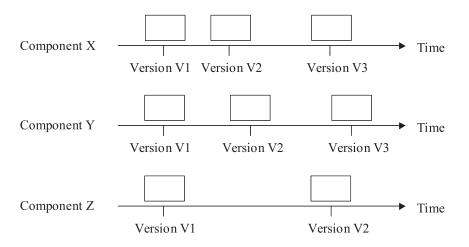

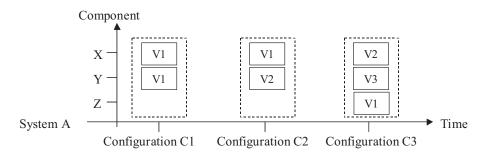

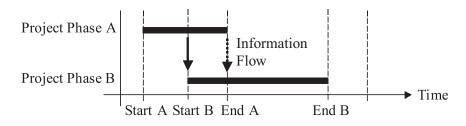

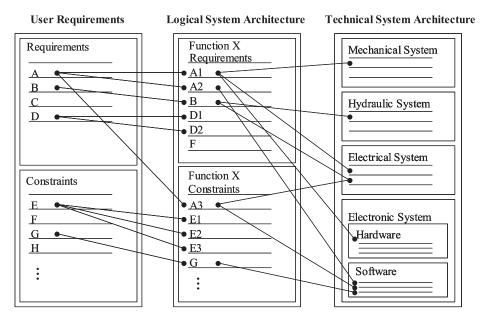

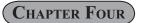

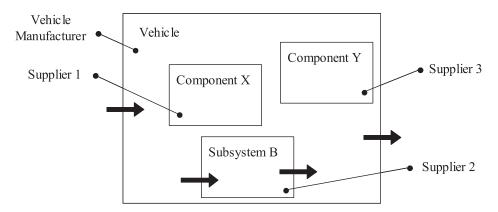

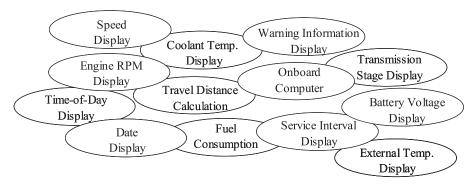

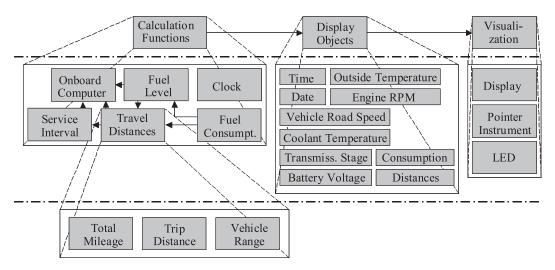

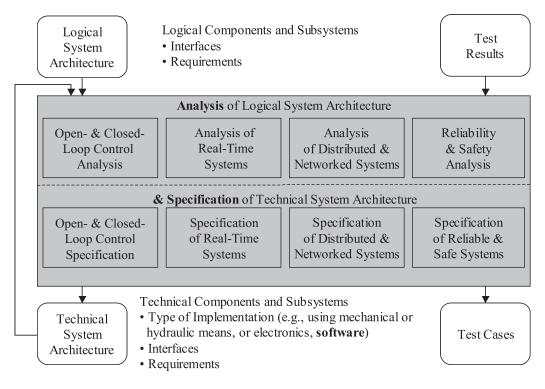

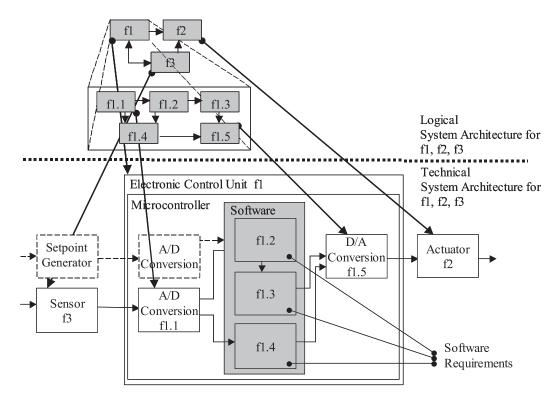

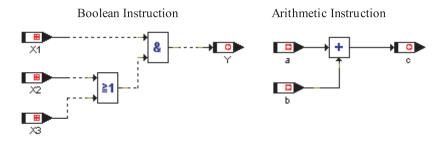

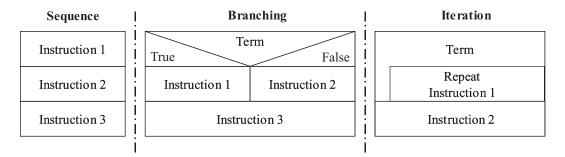

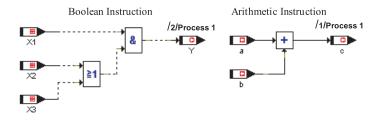

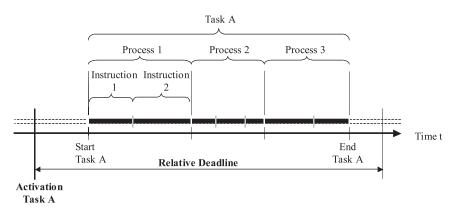

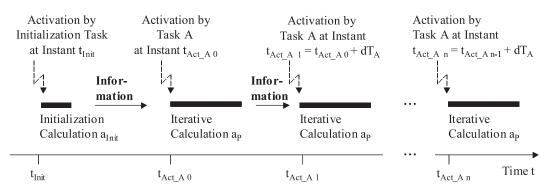

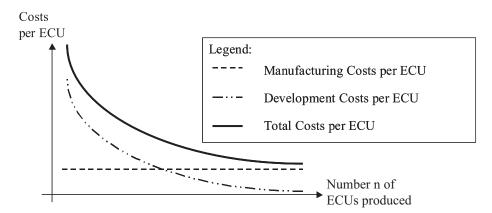

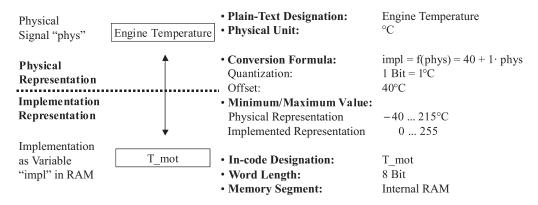

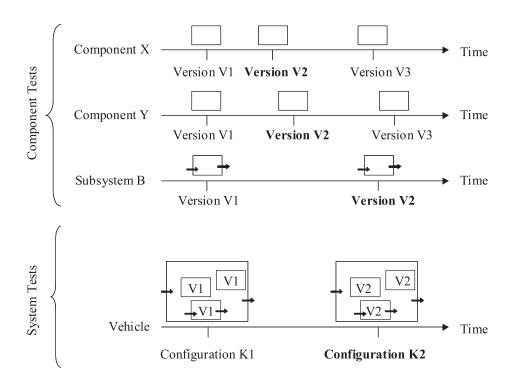

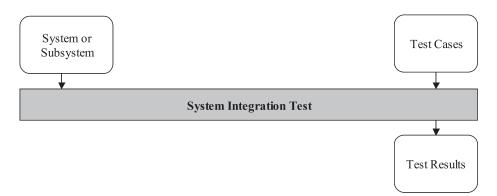

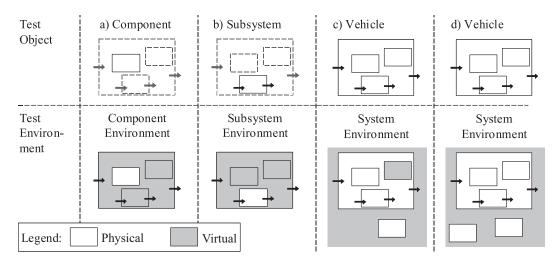

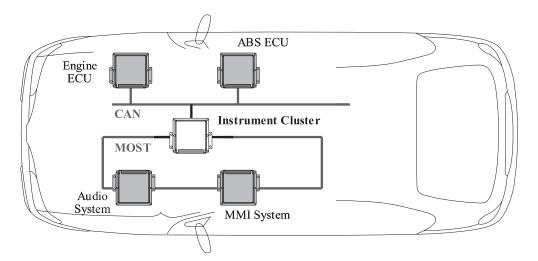

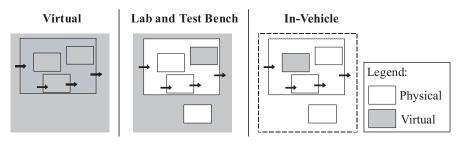

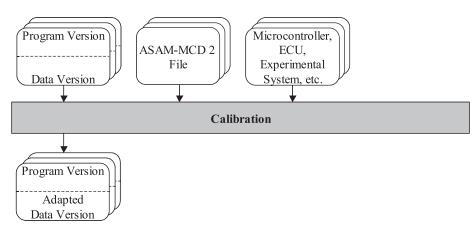

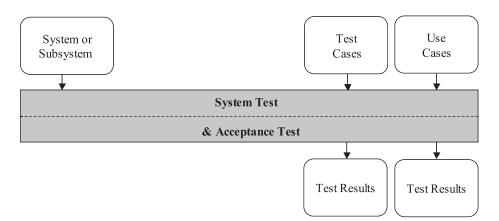

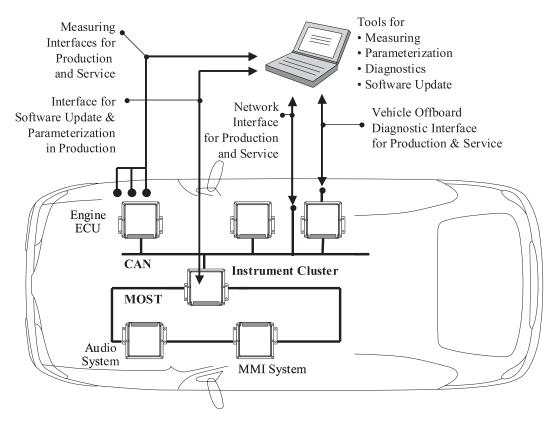

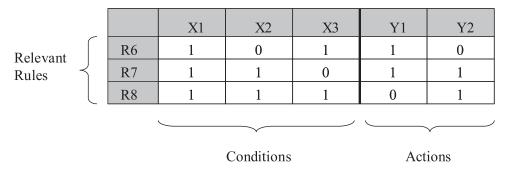

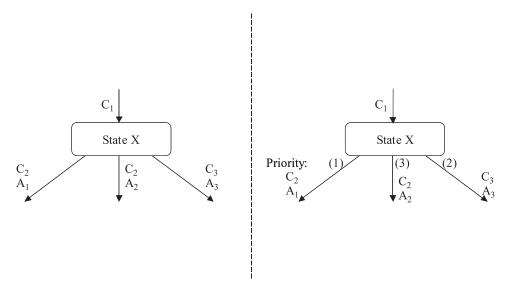

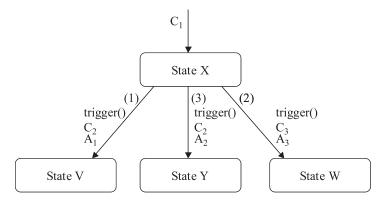

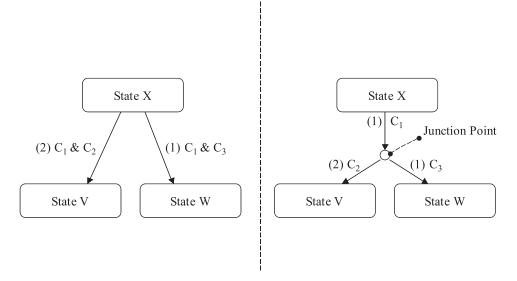

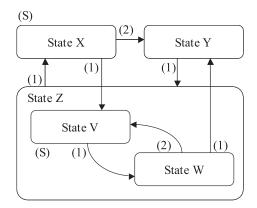

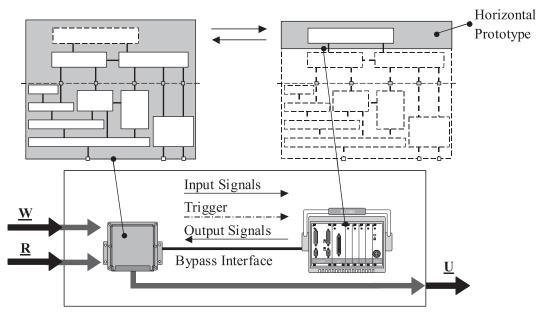

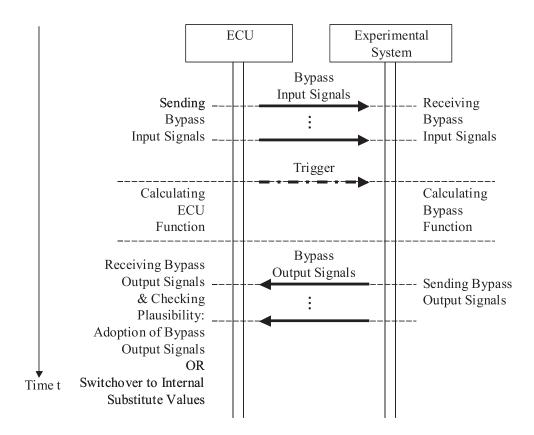

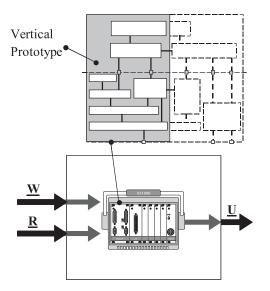

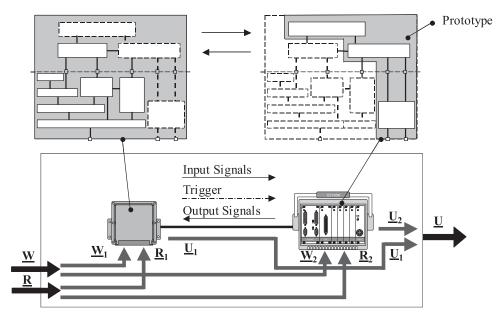

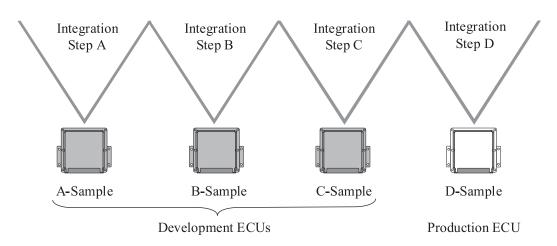

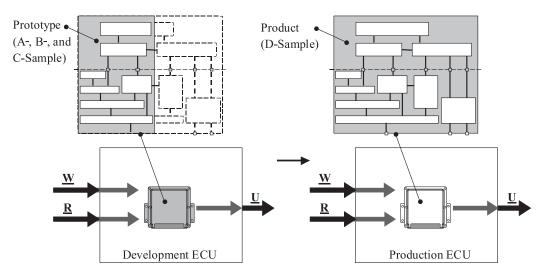

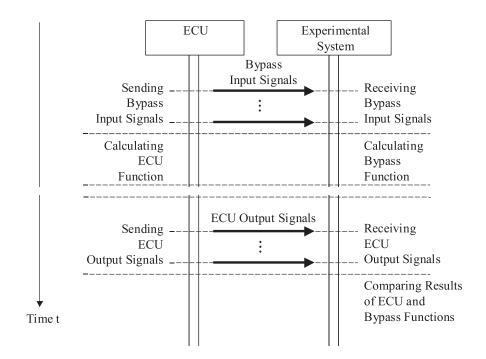

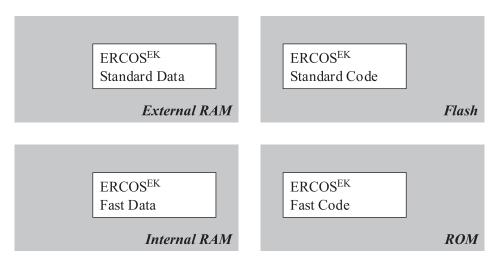

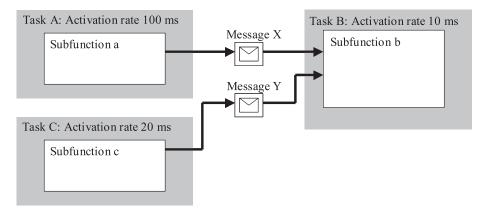

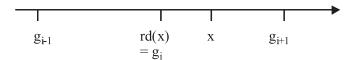

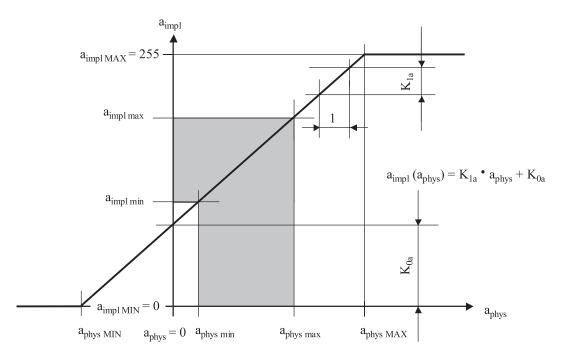

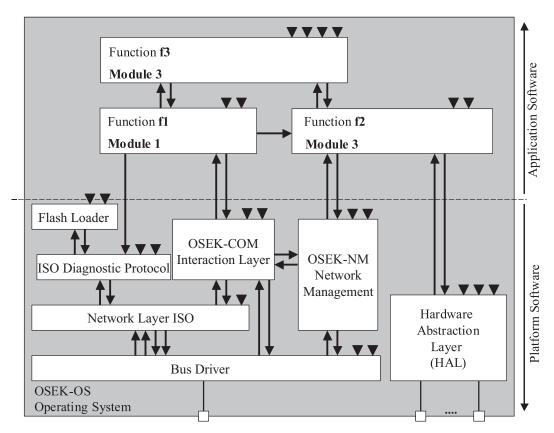

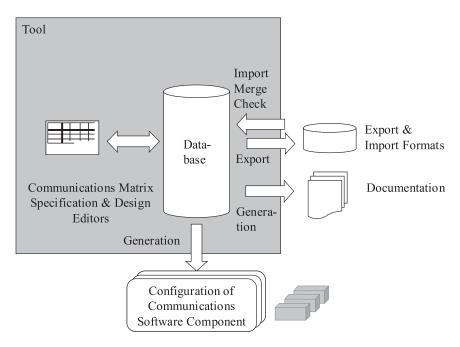

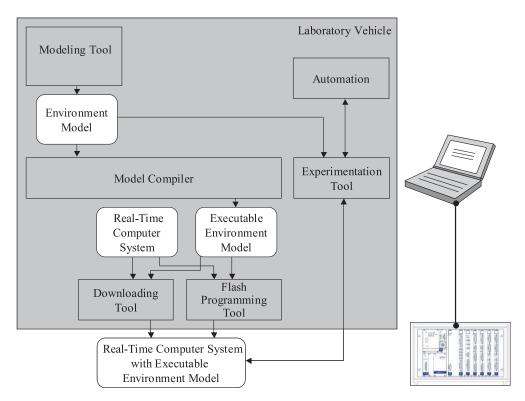

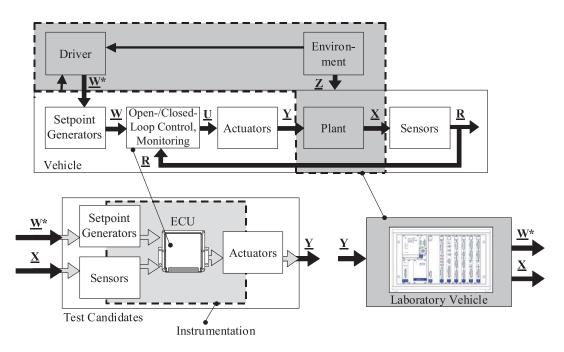

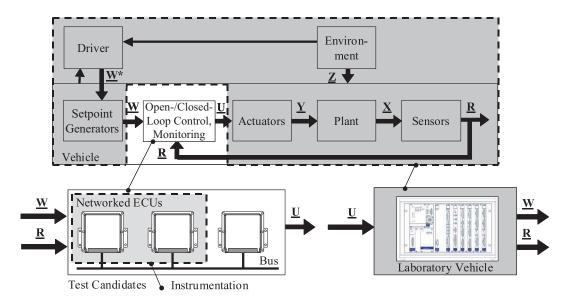

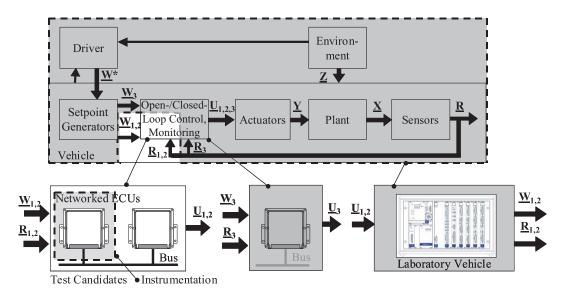

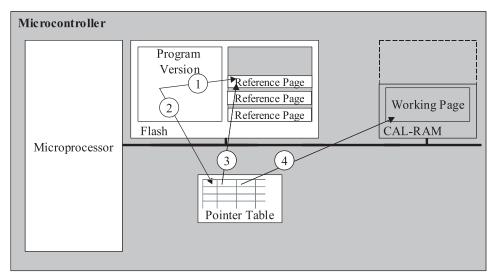

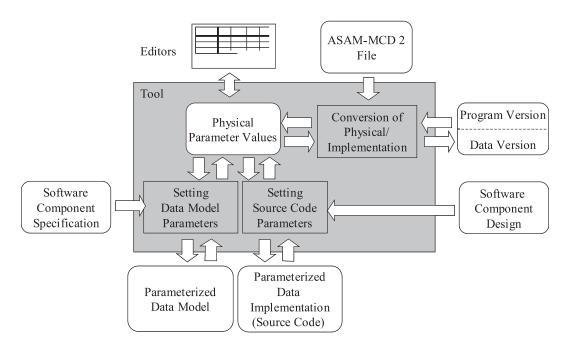

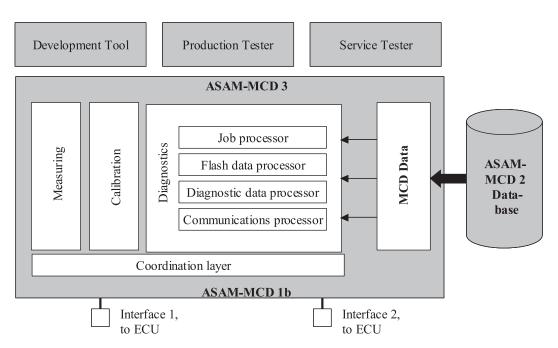

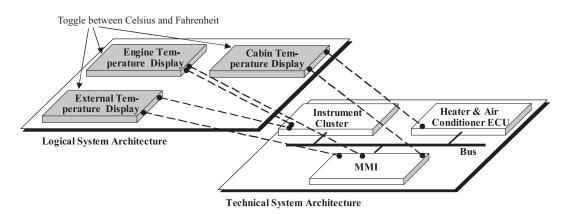

Fig. 1-5. Interfaces of a gasoline-engine ECU. (Ref. [6])